1.O circuito sequencial da FSM mostrado na Fig.1 tem uma entrada X e uma saída Z. Considere que o estado inicial da FSM é igual à representação binária do terceiro maior dígito do seu CPF e a sequencia em binário de X é igual `a representação BCD dos tres dígitos mais significativos do CPF. Então, complete o preenchimento da tabela de transição da FMS.

Solução

Fig.1

PS |

ENTRADA/SAÍDA |

NS |

Q2Q1Q0 |

X/Z |

Q2Q1Q0 |

/ |

||

/ |

||

/ |

||

/ |

||

/ |

||

/ |

||

/ |

||

/ |

||

/ |

||

/ |

||

/ |

||

/ |

2.A arquitetura simplificada do processador da Fig.2 tem quatro instruções PARAR, SOMAR, SUBTRAIR e TRANSFERIR, cujos códigos de operação estão mostrados abaixo. Na memória do processador tem um programa armazenado a partir do endereço 000000 cujo conteúdo em linguagem binária está mostrado abaixo. Sabendo que nas posições de memória 110000 até 110101 tem os conteúdos mostrado, determine o conteúdo em binário das posições de memória 110010, 110011, 110100, 110101, e do registrador de instruções IR, após a conclusão do programa. Suponha todos registradores resetados , inicialmente.

Solução

|

Endereço |

Conteúdo |

Comentários |

000000 |

01110000 |

|

000001 |

10110001 |

|

000010 |

10110001 |

|

000011 |

01110011 |

|

000100 |

01110100 |

|

000101 |

11110101 |

|

000110 |

01110101 |

|

000111 |

01110101 |

|

001000 |

11110101 |

|

001001 |

00000000 |

|

... |

... |

|

110000 |

XX |

dígitos de controle do CPF em BCD |

110001 |

YY |

16 em complemento-de-dois |

110010 |

ZZ |

-85 em complemento-de-dois |

110011 |

VV |

45 em complemento-de-dois |

110100 |

UU |

36 em complemento-de-dois |

110101 |

WW |

-35 em complemento-de-dois |

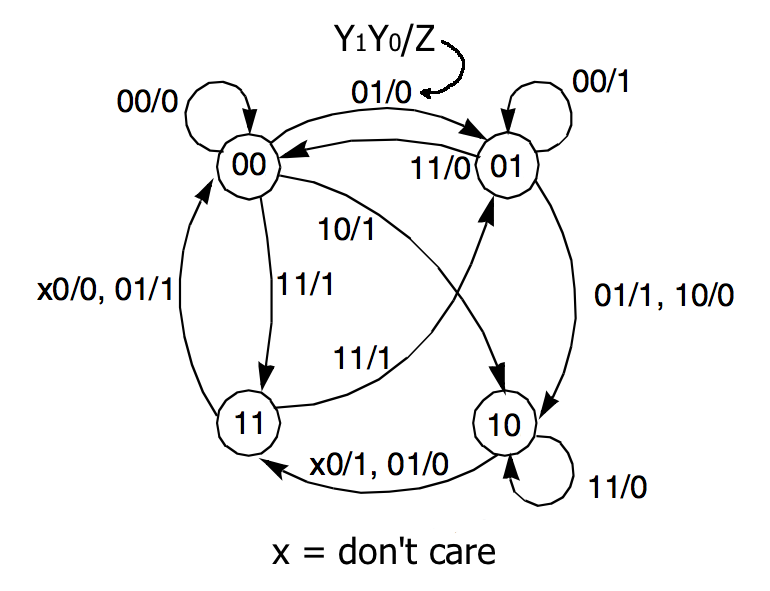

3.Um circuito sequencial FSM apresenta o diagrama de estados mostrado na Fig.3 abaixo. A FSM tem duas entradas Y1Y0 e uma saída Z síncronas. Considerando que a entrada Y1 é igual à sequência de bits dos cinco dígitos mais significativos e Y0 é igual à sequência de bits dos cinco dígitos menos significativos do número de seu CPF, em código BCD, determine a tabela de estados da FSM. Considere que os bit mais siginificativos são o primeiro valor de Y1Y0 na sequência e x representa uma entrada don't care. Se seu CPF é par, o estado inicial deve ter atribuição de estado com paridade ímpar; se seu CPF é ímpar, o estado inicial deve ter atribuição de estado com paridade par, e siga a sequencia determinada pelas entradas Y1Y0 do seu CPF.

Solução

PS |

Y1Y0 |

Z |

NS |

4. A tabela abaixo mostra uma sequencia de microinstruções executadas para a arquitetura da Fig.4. A locação de memória BC tem a representação BCD dos tres número mais significativos do CPF ( se o CPF é ímpar ) e igual a representação BCD dos tres número menos significativos do CPF ( se o CPF é par ). Após a conclusão do microprograma, determine o conteúdo binário das posição da memória BC, dos registradores ACC, F, GPR e MAR. Inicialmente, o conteúdo do registrador acumulador ACC é igual a 000H, o conteúdo do registrador GPR é igual a xBCH, onde x é don't care.

Solução

Fig.4

|

ACC = _____________ F = ___________ GPR = _____________ MAR = ____________BC = _____________

5.A Fig.5 mostra o controlador de registrador de deslocamentos e a arquitetura do processador controlado. Sabendo que os registradores são de 8-bits e inicialmente α tem os dois dígitos mais significativos do seu CPF, em hexadecimal, e β está com 10011000, desenhe o diagrama de fluxo, associando cada estado à designação dos flip-flops do controlador.

Solução

Fig.5

Atualizada em