1.O circuito sequencial da FSM mostrado na Fig.1 tem uma entrada X e duas saídas ZS. Considere que o estado inicial da FSM é igual à 001(CPF par) e 000(CPF ímpar) e a sequencia em binário de X é igual `a representação BCD dos tres dígitos mais significativos do CPF. Então, complete o preenchimento da tabela de transição da FMS.

Solução

PS(ABC) |

||||||||||||

X |

||||||||||||

NS(ABC) |

||||||||||||

ZS |

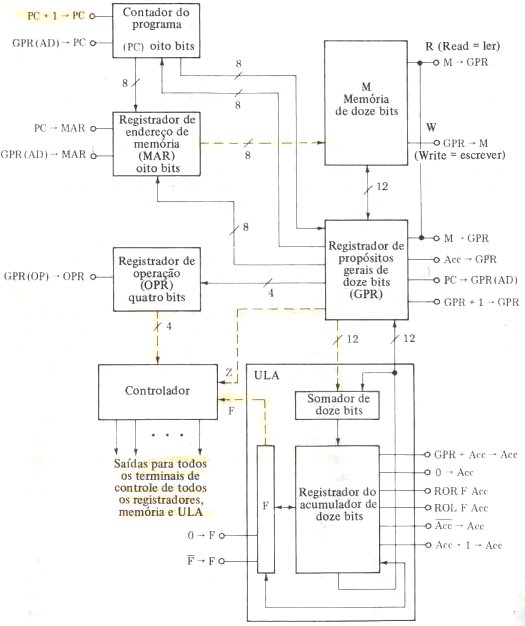

2.No local 11H da memória há a instrução 'somar ao acumulador o operando cujo endereço deve ser encontrado em uma posição de memória 1FH'. Este operando tem valor igual à representação BCD dos tres dígitos mais significativos de seu CPF, o contúdo da posição 1FH é igual a representação BCD dos dígitos de controle do seu CPF e o número no acumulador é igual a 000H. Suponha que o código da instrução é AH. Iniciando no instante da conclusão da instrução anterior, determine em binário o conteúdo da cada registrador(PC, MAR, OPR, GPR, ACC, F) da Fig.2, após o último ciclo de clock para que a instrução seja concluída e preencha a tabela abaixo.

Solução

Fig.2

Clock |

Microoperação |

PC |

MAR |

OPR |

GPR |

ACC |

F |

k |

- |

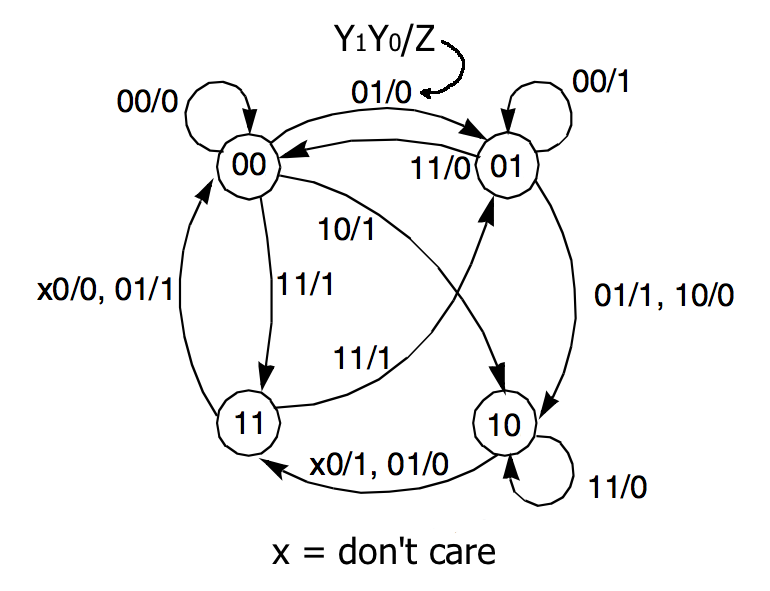

3.Um circuito sequencial FSM apresenta o diagrama de estados mostrado na Fig.3 abaixo. A FSM tem duas entradas Y1Y0 e uma saída Z síncronas. Considerando que a entrada Y1 é igual à sequência de bits dos cinco dígitos mais significativos e Y0 é igual à sequência de bits dos cinco dígitos menos significativos do número de seu CPF, em código BCD, determine a tabela de estados da FSM. Considere que os bit mais siginificativos são o primeiro valor de Y1Y0 na sequência e x representa uma entrada don't care. Se seu CPF é par, o estado inicial deve ter atribuição de estado com paridade ímpar; se seu CPF é ímpar, o estado inicial deve ter atribuição de estado com paridade par, e siga a sequencia determinada pelas entradas Y1Y0 do seu CPF.

Solução

PS |

Y1Y0 |

Z |

NS |

4.Na arquitetura do processador abaixo, está sendo empregada uma memória com capacidade igual a 64K palavras e cada palavra com 22 bits de comprimento. Então responda:

(a)Qual é o número de instruções que podem ser incorporados ao processador?

(b)Qual o tamanho, em bits, dos registradores PC, MAR, OPR e GPR?

Solução

Fig.4

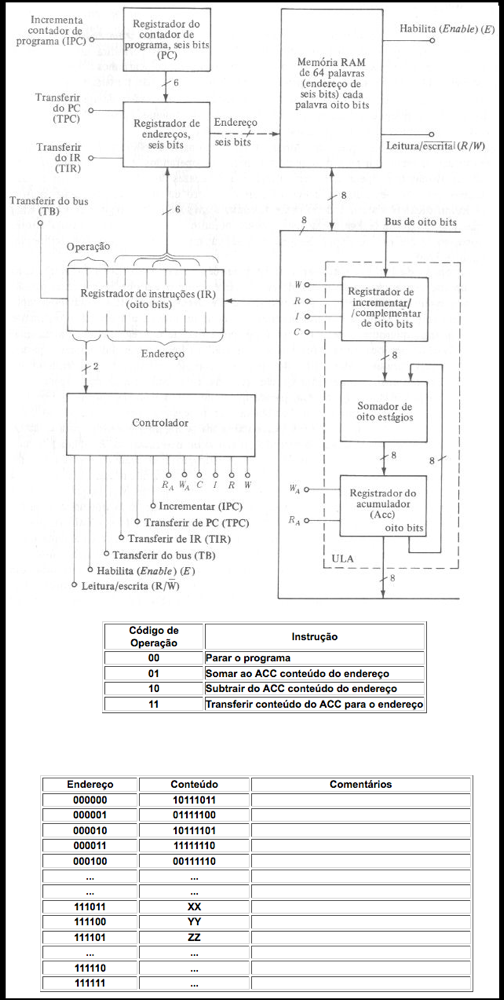

5.A arquitetura simplificada do processador da Fig.5 tem quatro instruções PARAR, SOMAR, SUBTRAIR e TRANSFERIR, cujos códigos de operação estão mostrados abaixo. Na mmória do processador tem um programa armazenado a partir do endereço 000000 cujo conteúdo em linguagem de máquina está mostrado abaixo. Sabendo que nas posições de memória 111011, 111100 e 111101 tem a representação BCD dos 6 dígitos mais significativos do seu CPF, determine o conteúdo da locação de memória 111110 após a conclusão do programa.Justifique.

Solução

Fig.5

Atualizada em