Roteiro

- As questões deste guia de estudos foram escolhidas de provas anteriores e do livro texto, para preparar você para a segunda prova do curso no Semestre 2023.2

- Leia o assunto relativo a cada questão no livro texto(aconselhável), na homepage ou em notas de aulas, antes de tentar a solução.

- As soluções são descobertas enquanto tenta resolver as questões. Se cometer alguns erros , considere isto parte do processo de aprendizagem.

- Tente resolver sem qualquer ajuda externa(livro, anotações ou colegas).

- Um melhor rendimento é obtido se você resolver cada questão, assim pode medir seu nível de aprendizado.

- Para cada problema determine uma solução completa, incluindo tabelas, equações e circuitos.

- Simplifique as equações dos problemas que exigem simplificação.

- Após resolver os exercícios, verifique sua solução, comparando com outras soluções de colegas e, por último, com as respostas, clicando nos links Solução, abaixo do enunciado de cada questão.

1.

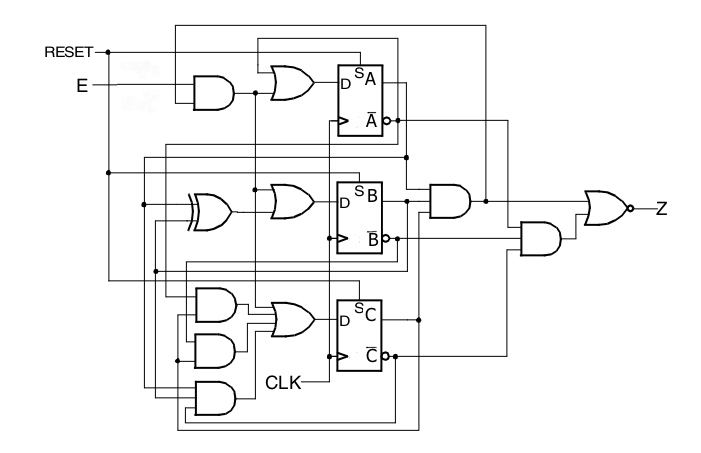

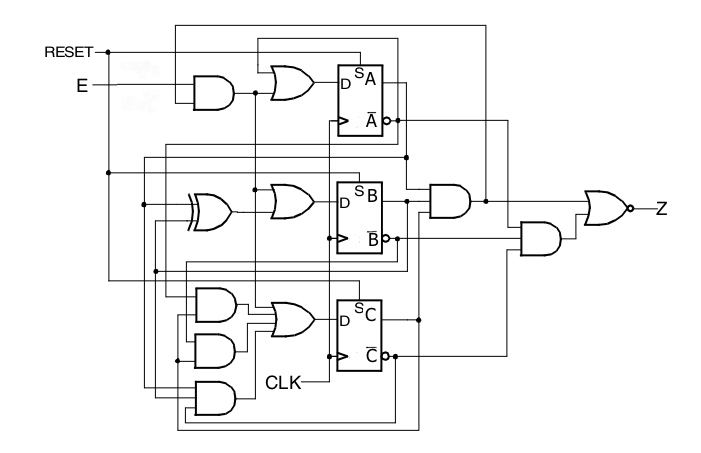

O circuito sequencial da FSM mostrado na Fig.1 tem uma entrada E e uma saída Z. Considere que o estado inicial da FSM EABC é igual `a representação BCD do segundo dígito mais significativos do CPF(CPF par) e EABC é igual `a representação BCD do segundo dígito menos significativos do CPF(CPF ímpar) e RESET igual a 0. Então, determine os estados e saídas da FSM depois de 5 pulsos de clock.

Solução

Fig.1

EABC |

ESTADO INICIAL = |

CLK |

1 |

2 |

3 |

4 |

5 |

NS(ABC) |

|

|

|

|

|

Z |

|

|

|

|

|

2.

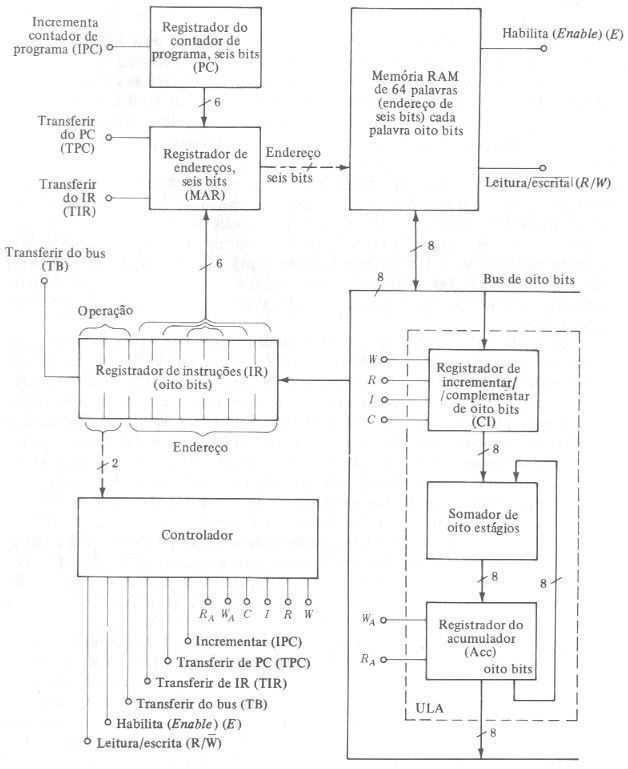

A arquitetura simplificada do processador da Fig.2 tem a posição da memória 00H gravada com a representação BCD( A7A6A5A4A3A2A1A0 ) dos dois dígitos menos significativos do CPF. Considere que o endereço da memória A5A4A3A2A1A0 está gravado com a representação BCD dos dois números mais significativos do CPF. Após a execução da sequência de microoperações mostradas, indique, em binário, o conteúdo dos registradores PC, IR, CI, ACC e MAR depois da execução da última microoperação. Considere que todos os demais registradores inicialmente estão resetados.

Solução

Clock |

Microoperação |

Comentários |

1 |

TPC |

|

2 |

E, R/W`, TB |

|

3 |

IPC |

|

4 |

TIR |

|

5 |

E, R/W`, W |

|

6 |

R, WA |

|

7 |

R, WA |

|

8 |

C |

|

9 |

I |

|

10 |

R, WA |

|

Fig.2

3.

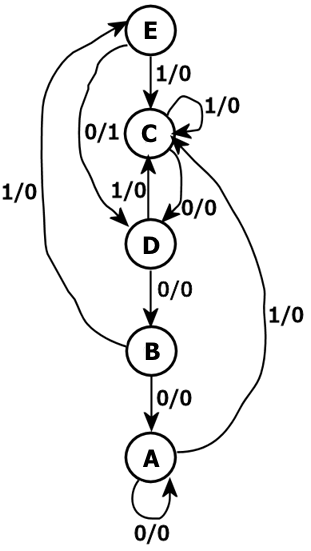

O controlador de um sistema digital apresenta um diagrama de fluxo mostrado na Fig.3, formado por uma FSM síncrona, tipo Mealy, com cinco estados A, B, C, D, E, uma entrada X e uma saída Z. Considere que a entrada X é igual a sequencia de bits (do MS para o LS) formada pela representação BCD dos cinco dígitos mais significativos de seu CPF, então complete a tabela de estados. Se seu CPF é par, o estado inicial(PS) será o estado E, e seu CPF é ímpar, o estado inicial(PS) será o estado C.

Solução

4.A Fig.4 mostra o controlador de registrador de deslocamentos e a arquitetura do processador controlado. Sabendo que os registradores são de 8-bits e inicialmente registrador α tem os dois dígitos mais significativos do seu CPF, em BCD, e registrador β está com os dois dígitos de controle(em BCD) do seu CPF, diga quais os conteúdos, em binário, dos registradores α, β , CI, ACC e FFs ABCDEFX (em binário), depois da última microoperação realizada.

Solução

Fig.4

Atualizada em

12/03/24