Dispositivos Logicamente Programáveis(PLDs-Programmable Logic Devices)

Existe uma grande variedade de CIs com diversas funções lógicas e arranjos de circuitos lógicos em chips de diversos fabricantes. Porém existem desvantagens em empregar estes CIs em determinados circuitos e sistemas:

Reduzir o número de CIs em projetos de circuitos e sistemas apresenta as seguintes vantagens:

Um PLD, Programmable Logic Devices(Dispositivos Logicamente Programáveis), é um circuito integrado com um grande número de portas lógicas, flip-flops, e registradores que estão interconectados no chip.

Várias conexões de um PLD são elos fusíveis, semelhantes aos encontrados em PROMs e EPROMs, que podem ser queimados.A Figura 1a mostra a estrutura básica usada pelos CIs logicamente programáveis: um arranjo de portas AND e um arranjo de portas OR, cujas entradas podem ser interconectadas para produzir funções nas saídas das variávies de entrada.

|

|

Para melhorar a representação dos dispositivos PLDs, adota-se uma simbologia simplificada onde as várias entradas de uma porta são representadas por uma única linha e as conexões das variáveis de entrada às portas são indicadas por um ponto ou um X: um X indica um fusível intacto; um ponto representa um conexão fixa(não pode ser programada). A falta de quaisquer desses sinais no cruzamento de duas linhas indica que não há conexão. A figura ao lado mostra um exemplo dessa simbologia. |

|

Fig.1b |

|

Os PLDs são chamados programáveis porque a função específica do circuito integrado para uma aplicação é estabelecida pela queima seletiva de alguns fusíveis e deixando outros intactos.Este processo chama-se programação porque produz o padrão desejado de interconexões entre portas, FFs, registradores, contadores, etc., conforme as instruções do usuário. O processo de queimar os fusíveis pode ser feito pelo fabricante ou pelo usuário, empregando um programador de EPROMs. |

Fig.1c |

| Um PLD é constituído de um arranjo de portas AND de entrada(decodificador) e um arranjo de portas OR de saída (codificador). Os arranjos AND de entrada podem ser conectados às variáveis de entrada para formar os termos produtos necessários. As funções de saída do circuito são obtidas interligando os termos produtos de saída do arranjo AND às entradas das portas do arranjo OR. |

|

Fig.2 |

Arquiteturas dos PLDsVárias arquiteturas são usadas para CIs PLDs. A arquitetura mais comum e utilizada é a PROM. A Figura 3a mostra uma PROM que funciona como um tipo de PLD.

Memórias Só de Leitura Programáveis(PROMs-Programmable Read Only Memories)

Nos dispositivos de memória só de leitura programáveis(PROMs), o arranjo AND é pré-definido em fábrica e somente o arranjo OR é programável.

Fig.3a

PROMs são utilizadas quando as equações precisam um grande número de termos produtos. As PROMs são geralmente consideradas dispositivos de memória onde cada endereço aplicado na entrada retorna uma palavra programada no dispositivo.

A Figura 3b mostra uma PROM de quatro entradas que são decodificadas pelo arranjo AND, onde cada porta gera um dos dezesseis minternos das variáveis de entrada.As conexões da variáveis de entrada ao arranjo AND são fixas, ou seja, não-programáveis, enquanto que as conexões das linhas de saída dos mintermos às portas OR são todas completamente programáveis.

|

|

Para programar a PROM a fim de gerar a função O3 indicada, o primeiro passo é escrever a função como um soma padrão de produtos, conforme mostra a tabela verdade. Observe que a programação consiste em manter intactos os fusíveis dos mintermos cujas linhas tem 1 na tabela verdade e queimar os fusíveis nas linhas que iguais são 0. |

Fig.3c |

| Os arranjos PALs têm somente os arranjos AND programáveis enquanto os arranjos OR são pré-conectados em fábrica, então todas as portas AND podem ser programadas para gerar o termo produto das variáveis de entrada e seus complementos(Figura 5a). Como as entradas das portas OR são fixas, então limita as funções da saída ao número de mintermos ligados nas entradas das portas OR. Caso seja necessários mais mintermos para gerar uma função, não será possível programar. Embora sejam menos flexíveis que PLAs, as PALs são mais rápidas porque as conexões pré-configuradas levam menos tempo para chavear que as conexões programadas. |

|

Fig.5a |

A Figura 5b mostra uma configuração típica para uma PAL com quatro entradas e quatro saídas. Sendo que cada porta OR tem suas entradas ligadas a quatro linhas de termos produtos, então só pode gerar funções de no máximo quatro mintermos.

|

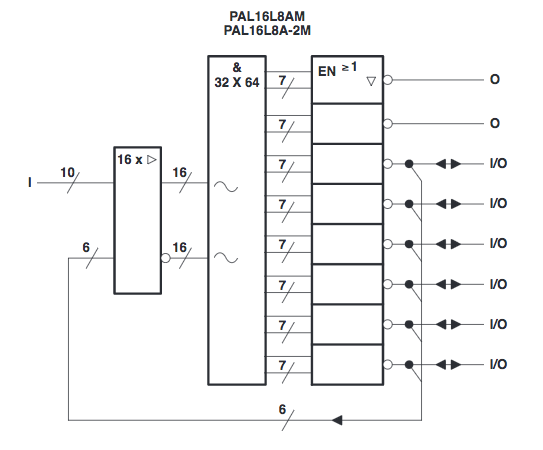

Como exemplo de um CI PAL veja o circuito integrado PAL16L8AM, da Texas Instruments, Inc., que tem 10 entradas lógicas e 8 funções de saída. Cada porta OR tem 7 entradas fixas que são saídas de 7 portas AND. Assim, pode gerar funções com até 7 termos produtos.

Fig.5c - PAL16L8AM - Texas Instruments

Arranjos de Portas Programáveis em Campo(Field Programmable Gate Array - FPGAs)

As FPGAs oferecem um número de blocos lógicos configuráveis que têm lógica combinacional programável e registradores para circuitos seqüênciais. Existe um conjunto de blocos de entrada/saída que pode ser configurado como entrada, saída e bidirecional. As saídas são tri-state e os registradores podem armazenar dados de entrada ou de saída.todos os blocos lógicos podem ser conectados para implementar qualquer função lógica desejada.Cada bloco lógico está conectado a um número determinado de matrizes de conexões programáveis, que, por sua vez, estão ligadas a um número de matrizes de chaveamento programáveis.Programando as conexões apropriadas, cada bloco pode fornecer uma variedade de funções lógicas combinacionais e/ou seqüênciais.As matrizes de conexões programáveis são usadas para estabelecer ligações entre entradas e saídas dos blocos lógicos, enquanto as matrizes de chaveamento programáveis são empregadas para rotear os sinais entre as várias matrizes de conexões.

|

Devido à variedade de arquiteturas, dispositivos FPGAs precisam de ferramentas de programação específicas do fabricante para a programação.

Características dos PLDs

Vários dispositivos PLDs têm saídas com buffers tri-state comandados por uma única linha de habilitação, requerendo apenas um pino de entrada do dispositivo.

Fig.6a

Uma caracterísitica que vários PLDs apresentam é saída com polaridade programável que possibilita a inversão dos níveis lógicos de saída do dispositivo.

|

Alguns dispositivos PLDs são construídos de modo que as saídas tri-state são realimentadas para as entradas do arranjo AND.

Fig.7

No exemplo acima, o PLA tem três entradas a, b e c e três saídas w, x e y, porém foi programado como quatro entradas e somente duas saídas. Observe que o buffer da saída y foi desconectado do sinal de controle de habilitação e ligado ao nível lógico alto, permanecendo sempre habilitado. A saída y está agora configurada como a quarta entrada da PLA.

Como as saídas w e x continuam a funcionar como funções de saída, então os elos fusíveis de realimentação são queimados para assegurar que não terão efeito nas entradas.

Certos tipos de PLDs são equipados com registradores nas saídas e outros com latches.Dependendo do dispositivo, os registradores(ou latches) podem ser fornecidos em todas as saídas ou em grupo de saídas. Em geral, é possível não utilizar os registradores de saídas através do uso de multiplexadores construídos no PLD.Este tipo de PLD é denominado sequenciador lógico programável.

Fig.8

Programação de PLDs

Os PLDs são programados e testados utilizando equipamentos programadores e programas específicos desenvolvidos para esta finalidade.Usando o programa, o usuário pode informar ao programador, através do microcomputador, as equações logicas que deseja programar no PLD.O programa gera o mapa de queima dos fusíveis e os dados de testes e envia para o programador realizar a programação.A Figura 9 abaixo mostra o fluxograma típico de programação e teste de um PLD.

|

Visite estas páginas sobre PLDs |

|

|

Dispositivos de Lógica Programável (PLD’s) |

Atualizada em