Memórias - Expandindo Capacidade e Tamanho da Palavra

Em várias aplicações a capacidade ou tamanho da palavra necessária para memória ROM ou RAM não pode ser atendida por somente um CI de memória.Em lugar, vários chips de memórias devem ser combinados para fornecer a capacidade ou tamanho da palavra requerida.

Aumento do Tamanho da Palavra

O aumento do tamanho da palavra significa aumentar o número de bits na palavra.Isto pode ser obtido ligando os circuitos integrados de memórias conforme abaixo.

Memória 16X8-palavrasXbits com CIs 16X4-palavrasXbits

|

|

Memória 8K X 8-palavrasXbits com CIs 2K X 8-palavrasXbits

|

| Questões de Revisão Resolva um teste on-line sobre o assunto acima e veja seu aproveitamento na matéria. |

|---|

Outros Links sobre Memórias: |

Além de constituírem a memória principal de alta capacidade e velocidade dos processadores, os circuitos integrados de memórias semicondutoras realizam funções especiais em computadores e outros equipamentos e sistemas digitais.

Memória Cache

A CPU da maioria dos computadores é muito mais rápida que as memórias DRAM da memória principal resultando em uma velocidade do clock do barramento menor que a taxa do clock da CPU. Então, a CPU pode processar instruções muito mais rápido que a taxa na qual as instruções são buscadas na DRAM. A fim de otimizar a velocidade da CPU, a memória deve suprir instruções na mesma velocidade. Isto significa que, a memória deve ser tão rápida e próxima da CPU quanto possível.

Para resolver o problema, uma pequena quantidade(Kbytes ou Mbytes) de SRAMs muito rápidas são fabricadas dentro da CPU. Esta memória armazenaria as instruções que a CPU usará imediatamente.Esta memória é chamada o cache da nível 1(L1). O objetivo do sistema de cache é assegurar que a CPU tenha o próximo bit de dados que irá precisar já carregado no cache no instate que a CPU vai buscar esse dado( chamado um cache hit, ou acerto de cache).

Como as CPUs atualmente tem vários núcleos, então cada núcleo tem seu próprio cache L1, que dividem a mesma interface de barramento, integrada no mesmo CI. Um outro bloco de memória de vários Mbytes, associado à interface de barramento comum, é denominado de cache L2, pode ser fabricado no mesmo CI, e supre todos os caches L1 da CPU.

Os dados e instruções do cache L2 podem ser supridos pela memória principal DRAM ou por um bloco de memória rápida entre o cache L2 e a memória principal DRAM. Esse bloco de memória é denominado cache L3 e está montado na placa.

Memória FIFO(First-In, First-Out)

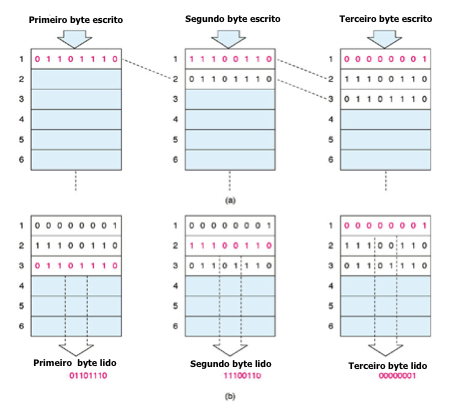

Em sistemas de memória FIFO, os dados são lidos na mesma ordem na qual foram escritos na memória. Ou seja, a primeira palavra que foi escrita no bloco de memória será a primeira palavra que será lida do bloco de memória.

Fig.4

A operação da memória FIFO é controlada pelo registrador apontador de endereços que mantem os endereços onde os dados são escritos e de onde eles serão lidos. Observe que os dados são sempre escritos na posição inicial do bloco de memória FIFO e, os dados escritos anteriormente são deslocados para as posições de memórias subsequentes.

Uma memória FIFO pode ser usada como um buffer de transferência de dados entre dispositivos de baixas velocidades e CPUs de altas velocidades. Enquanto a memória FIFO é preenchida(escrita) assincronamente, a CPU realioza outras tarefas, e ao completar a memória FIFO, a CPU faz a leitura rapidamente e processa os dados.

Buffer Circular

O buffer linear são buffers que serão lidos somente quando estiverem completamente preenchidos e nenhum dado será escrito até o buffer ser completamente lido(esvaziado). Nenhuma informação 'velha' será perdida.

O buffer circular são blocos de memórias que armazenam os últimos n valores escritos, onde n é o número de endereços de memórias do buffer. Cada vez que um novo dado é escrito no buffer circular, então ele é escrito em cima(substitui) do dado mais velho. Os buffers circulares são endereçados por um contador de endereços MOD-N. Assim, quando o contador chega na maior contagem(endereço mais alto), então será reset e a próxima posição de memória a ser escrita será a mais baixa(menor).

Atualizada em