As memórias Flash foram uma resposta da indústria às memórias EPROM e EEPROM, com um produto que oferece as vantagens destas memórias sem o alto custo.

As duas principais arquiteturas de arranjos das memórias flash são Flash NOR e Flash NAND.

A memória Flash foi inventada pela Toshiba Corp.(pelo Dr. Engº Fujio Masuoka), em 1984.

Com base na invenção de Masuoka, a Intel Corp. comercializou memória Flash NOR de base comum em 1988.

A Toshiba Corp. introduziu a memória Flash NAND em 1988, que prometia um custo por bit menor do que a Flash NOR e uma programação mais rápida e alta taxa de apagamento de dados.

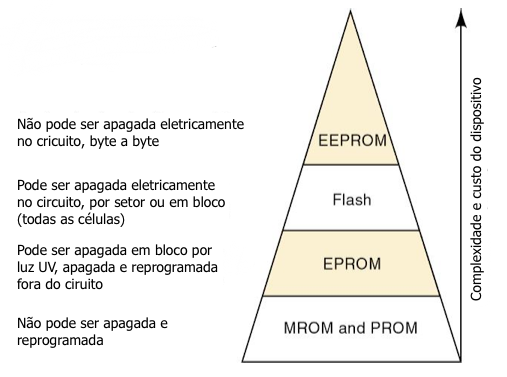

Memórias não voláteis - Custo e complexidade versus apagamento

Características das memórias Flash:

- Não-volátil

- Apagável eletricamente total ou por setor, no circuito

- Grande densidade

- Tempos pequenos de gravação e apagamento

- Alta velocidade de acesso

- Baixo custo

|

A célula de uma memória Flash é semelhante à célula de uma EPROM, e é constituída por um único transistor. Na memória Flash, uma fina camada de óxido de sílicio forma a porta do transistor, permitindo apagar eletricamente a memória e uma maior densidade que as EEPROMs, com um custo menor. A Fig.1 compara os dois tipos de células de memória, onde a camada de óxido entre a porta e o substrato é 100 Angstrons, aproximadamente, para a célula Flash e maior que 150 Angstrons para a EPROM. |

|

|

|

|

||

Fig.1 Célula Flash e Célula EPROM |

|

||

|

|

|

Fig.2 Célula Flash - Operação de Escrita |

Para apagar o conteúdo de uma célula Flash, a tensão de fonte(Source) é colocada em VPP=12 Volts, a porta(Control Gate) de controle é aterrada e o dreno(Drain) fica flutuando(Ver Fig.3).

Devido a grande tensão aplicada na fonte (em relação à tensão na porta), há uma atração dos elétrons negativamente carregados da porta flutuante para a fonte através da fina camada de óxido.

|

|

|||

Fig.3 Célula Flash - Operação de Apagar |

||||

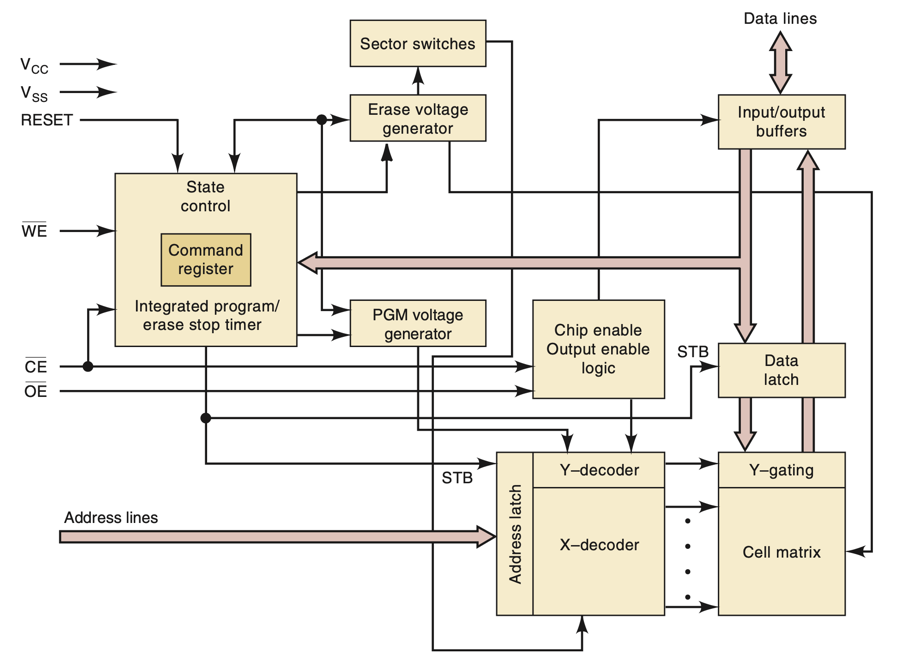

Memória Flash. Diagrama de Blocos

Tecnologia das memórias Flash: NOR e NAND

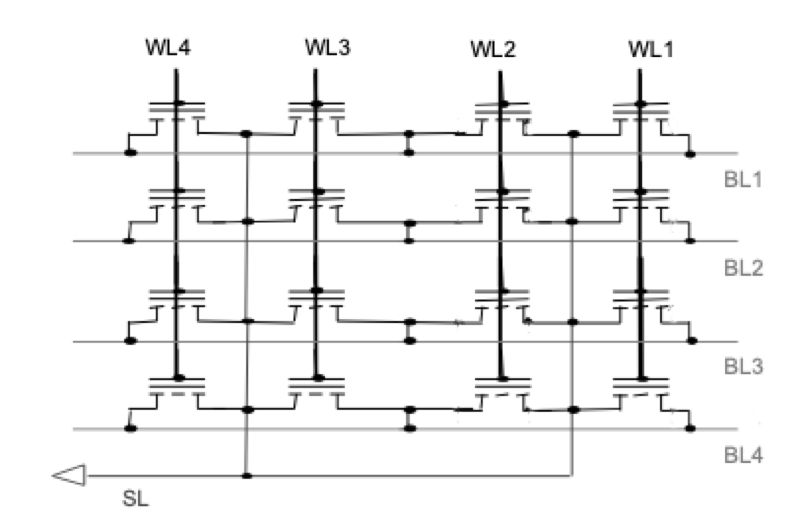

A tecnologia Flash NOR utiliza MOSFETS de porta flutuante (FGMOSFET) arranjados em paralelo entre a linha de bits(coluna da matriz de armazenamento) e o terra.

A Flash NOR é organizada por byte ou palavra.

A memória Flash NOR emprega uma arquitetura paralela em que cada célula pode ser acessada por meio de um contato (Fig.4).

O acesso direto à célula de bit é a razão para o desempenho de acesso aleatório superior da Flash NOR.

No circuito acima da Flash NOR, cada uma das linhas de palavras(wordlines) WL1, WL2, WL3, e WL4 controla os transistor MOSFET que liga a linha de bit(Bit Line - BL) ao terra. Se WL1=1 OU WL2=1 OU WL3=1 OU WL4=1(nível ALTO), então a linha de bit(BL) vai para o nível BAIXO(lógico 0).

A memória é chamada de Flash NOR porque se as entradas WL1=1 OU WL2=1 OU WL3=1 OU WL4=1(nível ALTO) então a linha de bit(saída) é igual a 0, ou seja, Bit Line=0, que é a lógica de funcionamento de uma porta NOR.

Observe que cada célula de bit(transistor MOSFET) é lida(Read) ou escrita(Write) independente dos outros transistores no grupo.

Características das Memórias Flash NOR |

||

Vantagens |

Desvantagens |

Aplicações |

| Acesso aleatório | Escrita lenta | Substituíção de EPROM |

| Escrita por bytes | Apagamento lento | Execução direta de programas da memória não-volátil |

| Endereçamento simples | Maior custo | Firmware de PCs, celulares, palmtops, PDAs |

A Fig.6 mostra a memória Flash NOR paralela M29W400DT, com capacidade de 4Mb, organizada como 512KbX8 ou 256KbX16 palavrasXbits, tensão de alimentação 3Vcc, para operações de leitura, apagamento e programação.

Essa Flash NOR pode ser lida do mesmo modo que memórias ROM ou EPROM.

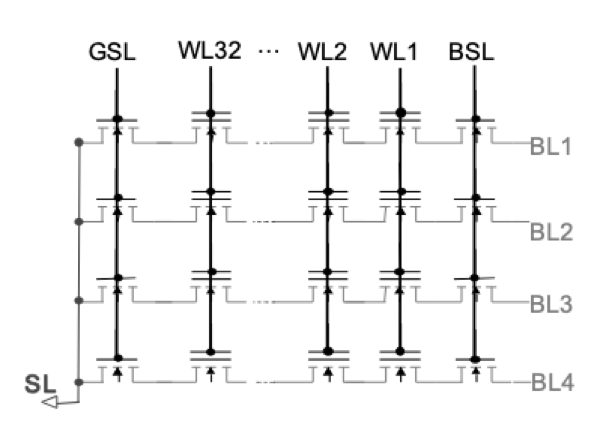

A tecnologia Flash NAND usa um grupo de FGMOSFETs em série uns com os outros, ligando a linha de bits(Bit Line - BL) com o terra.

Os dados armazenados em cada célula de bit são acessados em conjunto com as outras linhas de palavra (Word Line - WL) no grupo, ativadas por uma tensão de porta de controle suficiente para ligar todos os outros transistores, independente da carga armazenada na porta flutuante.

Ou seja todos outros transistores são colocados em condução, fornecendo baixa resistencia entre a fonte e o dreno e a célula de bit acessada controla a linha de bits.

Como as células de memória na Flash NAND são organizadas em série, a Fig.7 mostra 32 células de memória imprensadas entre grandes transistores selecionadores(GSL) e contatos(BSL).

O desempenho de acesso aleatório é lento devido ao fato de que não há contatos acessando diretamente as células de memória.

No entanto, como há apenas dois contatos a cada 32 células de memória, o tamanho efetivo da célula é muito menor do que a Flash NOR, resultando em um tamanho de chip menor e menor custo por bit.

Como todas as linhas de palavra WL1, WL2...WL32 devem ser ALTAS para que a linha de bits seja puxada para nível BAIXO, então o circuito comporta-se como uma porta NAND, dando o nome à memória Flash NAND.

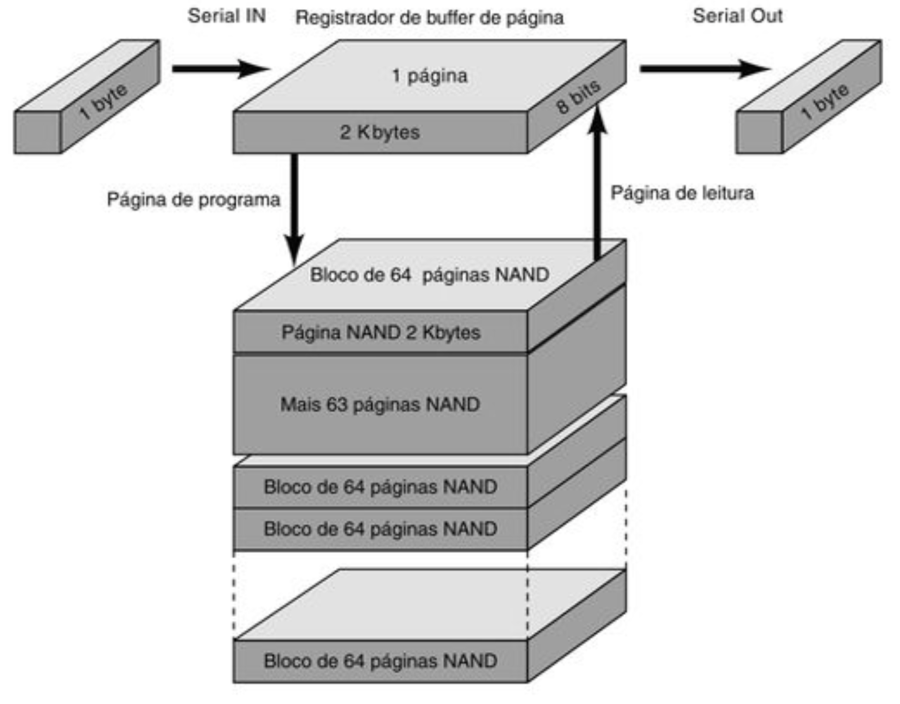

A memória NAND contém informações organizadas de uma maneira específica. Observando a figura abaixo, uma memória é dividida em páginas e blocos.

Um bloco é a menor unidade apagável.

Geralmente, há uma potência de dois blocos em qualquer dispositivo.

Cada bloco contém várias páginas.

O número de páginas dentro de um bloco é normalmente um múltiplo de 16 (por exemplo, 64, 128).

Uma página é a menor unidade endereçável para leitura e escrita.

Cada página é composta por área principal e área extra.

A área principal pode variar de 4 a 8 kB ou até 16 kB.

A área sobressalente pode ser usada para ECC (código de correção de erros) e ponteiros de sistema, e é da ordem de algumas centenas de bytes a cada 4 kB de área principal.

A Flash NAND exibe gravações de página rápidas devido à capacidade de gravar de 4 a 8kB simultaneamente, resultando em uma taxa de transferência de gravação sequencial muito alta.

Para qualquer operação em um dispositivo NAND, deve-se emitir o endereço onde se quer atuar.

O endereço é dividido em endereço de linha e endereço de coluna.

O endereço da linha identifica a página endereçada, enquanto o endereço da coluna é usado para identificar os bytes dentro da página.

Quando os endereços de linha e coluna são necessários, o endereço da coluna é fornecido primeiro, 8 bits por ciclo de endereço.

O primeiro ciclo contém os bits menos significativos.

Endereços de linha e coluna não podem compartilhar o mesmo ciclo de endereço.

O endereço da linha identifica o bloco e a página envolvida na operação.

O endereço da página ocupa os bits menos significativos.

O circuito Flash NAND tem velocidades de apagamento e programação rápidas e os dados são acessados em blocos. Porém, as memórias Flash NOR tem velocidade de leitura mais rápida e acesso aleatório.

A operação de programação da bit cell Flash NAND altera o potencial da porta flutuante das células selecionadas para um nível especificado, injetando cargas na porta flutuante.

A tensão de programação Vpp aplicada à linha de palavra da página selecionada é aumentada por um incremento constante Vstep para cada pulso de programação.

Isto aumenta as cargas na porta flutuante em uma quantidade que desloca Vth, tensão de limiar(threshold voltage), (Vth), das células em um incremento constante ΔVth.

Após cada pulso de programa, a página é lida e as células que atingiram o nível V especificado ou que não deveriam ser programadas são definidas para inibição de programa para os pulsos de programa consecutivos.

A operação do programa termina quando o Vth de todas as células for superior ao nível Vth alvo ou quando um limite geral de pulso do programa for atingido.

Assim, obtem-se diversos valores de Vth, correspodendo a diversos valores de carga na porta flutuante.

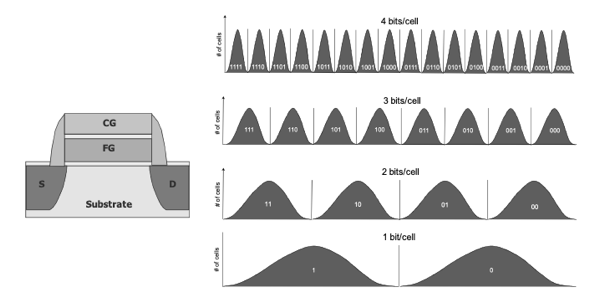

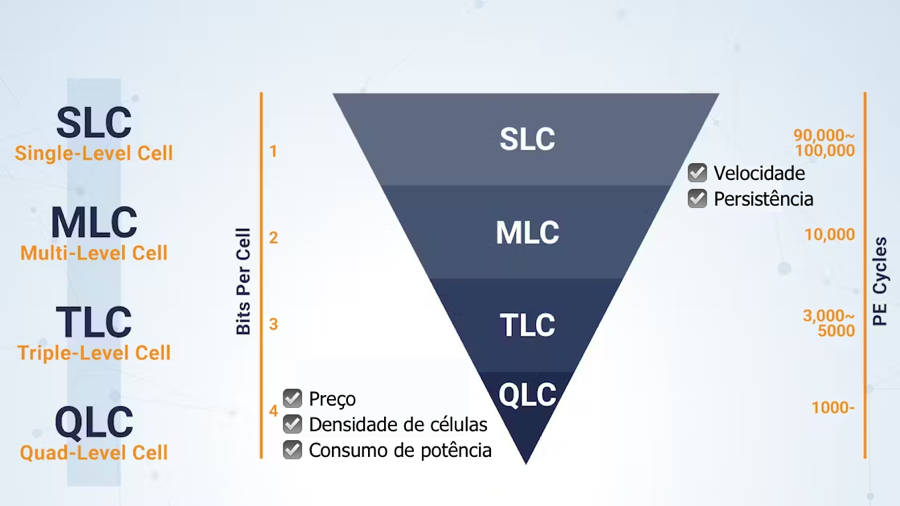

A memória Flash NAND SLC(Single Level Cell) convencional ou armazenamento de célula de nível único distingue entre um '1' e '0' por não ter nenhuma carga ou carga presente na porta flutuante da célula de memória flash.

Aumentando o número de níveis de limite de carga ou tensão de limiar(threshold voltage), (Vth), então mais de 1 bit por célula podem ser armazenados.

No entanto, o armazenamento de células multinível requer o posicionamento preciso dos níveis de carga, Vth, para que as distribuições de carga não se sobreponham, bem como a detecção precisa dos diferentes níveis de carga.

À medida que o número de níveis de Vth aumenta, o tempo necessário para programação e detecção precisas aumenta.

O armazenamento de dois bits por célula MLC(Multi Level Cell) é habilitado aumentando o número de níveis de Vth para quatro, representando 11, 10, 01 e 00.

Da mesma forma, aumentando o número de níveis de tensão de limiar(Vth) para oito e 16, então 3 bits por célula e 4 bits por célula de armazenamento estão habilitados.

O benefício do armazenamento de células multinível é que a capacidade de armazenamento pode ser aumentada sem um aumento correspondente na complexidade do processo de fabricação do chip de memória.

À medida que o número de níveis de tensão de limiar, Vth, aumenta, o tempo necessário para uma programação e detecção de bit precisa aumentar.

Os custos mais baixos associados à tecnologia de célula multinível não são gratuitos.

O custo mais baixo vem às custas de desempenho e retenção reduzidos.

Degradação significativa na persistência, retenção e desempenho de gravação ocorre com o aumento do número de bits por célula.

Memória Flash NAND célula multinível

As memórias Flash NOR e Flash NAND têm características igualmente significativas e diferenças de desempenho que afetam o tipo de aplicativo onde cada uma é mais adequada.

Além da capacidade, as memórias Flash NAND e NOR possuem características operacionais, de desempenho e de custo diferentes, conforme mostrado a seguir.

Memória Flash NAND SLCMX30UF1G16(18)AC

O chip MX30UF1G16(18)AC , fabricado pela Macronix International, de Taiwan, é um dispositivo de memória Flash NAND SLC de 1Gb.

Seus recursos Flash NAND padrão e qualidade confiável de ciclos típicos, que a torna mais adequada para código de sistema embarcado e armazenamento de dados.

O chip MX30UF1G16(18)AC é um dispositivo de plano único de 1Gb, que é composto por 64 páginas de (2.048 + 64) bytes em estrutura NAND de dois `strings` com 32 células conectadas em série em cada string.

A entrada de endereços, a entrada de comando e a entrada / saída de dados são gerenciadas pelos sinais CLE, ALE, CE#, WE#, RE# e WP#, conforme mostrado na tabela lógica abaixo.

Programar, Apagar, Ler e Redefinir são quatro modos de operação principais controlados por conjuntos de comandos.

A Fash NAND é o carro-chefe das memórias flash, amplamente usada para armazenamento de dados em massa de sistemas embarcados e dispositivos de armazenamento como SSDs.

Mas a Flash NOR desempenha um papel crítico no armazenamento de código de inicialização executável e para aplicativos que requerem leituras aleatórias frequentes de pequenos conjuntos de dados.

Ambos os tipos de memória flash continuarão a ser indispensáveis para o projeto de sistemas de computador, rede e armazenamento.

| Questões para Revisão Resolva algumas questões sobre o assunto de tecnologias de memórias FLASH. |

||

|

||

Atualizada em