Tabela do Conteúdo da ROM:  Fig.6 |

Equações do decodificador da ROM:

Fig.7-14 |

Equações do codificador da ROM:

Fig.15-18 |

|

||||||||||||||||||||||||||||||||

| Circuito Lógico da ROM | |||||||||||||||||||||||||||||||||||

O conteúdo de uma ROM com 8-palavras e 4-bits por palavras é mostrado na Fig.6. A tabela verdade para memória indica que a memória é um conversor de código de entrada(endereços A2A1A0) para outro código de saída(dados D3D2D1D0), isto é, um circuito decodificador em cascata com um circuito codificador. |

Fig.19 |

||||||||||||||||||||||||||||||||||

| O codificador de uma ROM pode ser implementado empregando uma matriz de diodos, em lugar de portas OR, desde que uma matriz de diodos realiza uma função OR. A Fig.20 mostra o circuito de duas portas OR com diodos: a primeira realiza Z=A+B e a segunda, a operação OR para qualquer número de variáveis de entrada. |

|

|||

Fig.20 |

||||

A Fig.21 abaixo mostra o codificador da ROM 8 X 4-palavrasXbits.

|

|

||

|

|

||

Fig.21 |

|

||

As memórias MROM têm suas locações de armazenamento programadas pelo fabricante de acordo com as especificações do cliente. As maiores desvantagens da MROM é que não pode ser reprogramada e só é econômica em grandes quantidades.

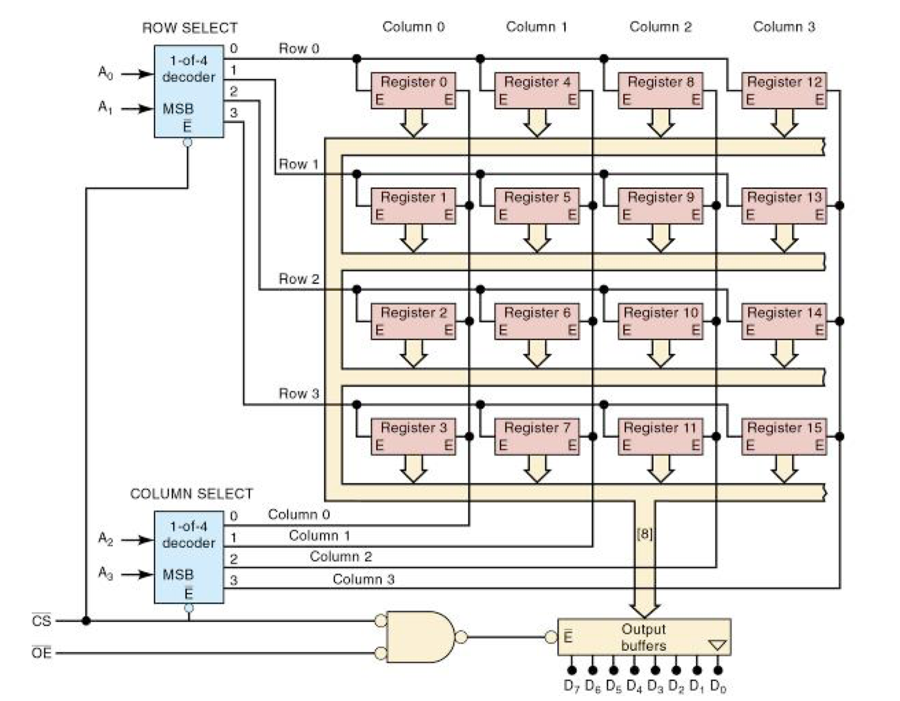

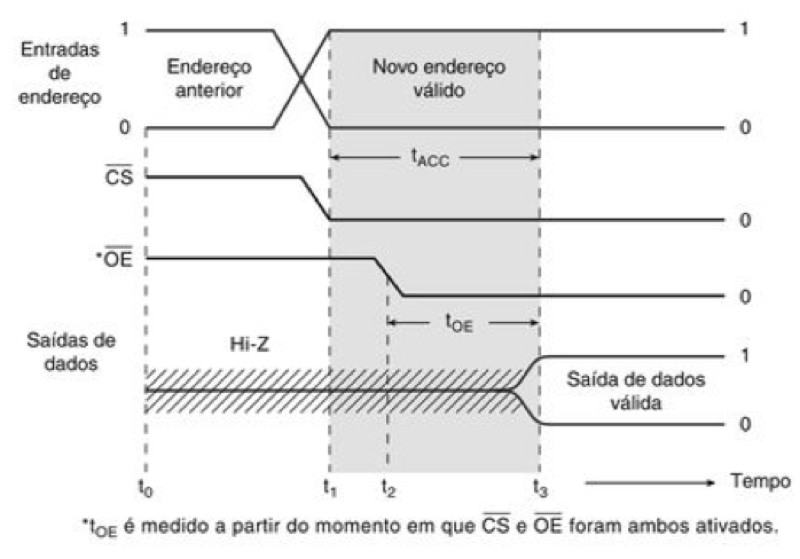

Fig.23

Arquitetura da ROM 16X8 palavrasXbits

No tempo t0, as entradas de endereços estão em níveis determinados, ALTO ou BAIXO e os sinais de habilitação chip select e output enable estão ALTOS, então as saídas de dados ficam em ALTA IMPEDANCIA(TRI-STATE).

Antes de t1, as entradas de endereços estão mudando para uma nova operação de leitura.

Em t1, o endereço é válido e chip select é ativado, BAIXO.

Em t2, chip select e output enable estão BAIXOS, habilitando os buffers de saída.

Em t3, as saídas passam de ALTA IMPEDANCIA para dados válidos armazenados no endereço de entrada.

O tempo de acesso tacc é igual ao tempo entre os instantes t1, quando o novo endereço é válido, e o instante t3, quando os dados de saída são válidos

| Diagrama de blocos e funções dos pinos |

|

||||

|

|

|

|||

Fig.24 |

|

||||

| Tempo de Habilitação do Circuito | |

| Tempo de Habilitação da Saída | |

| Tempo de Acesso após Endereço | |

| Tempo de Manutenção da Saída | |

| Tempo do Ciclo de Leitura |

| Questões para Revisão Resolva algumas questões sobre o assunto de tecnologias de memórias ROMs. |

|

|

Fig.25

A série TMS27PC256 são memórias de apenas leitura programáveis eletricamente (PROM) somente uma vez(OTP) organizadas como 32768 X 8- palavrasXbit.

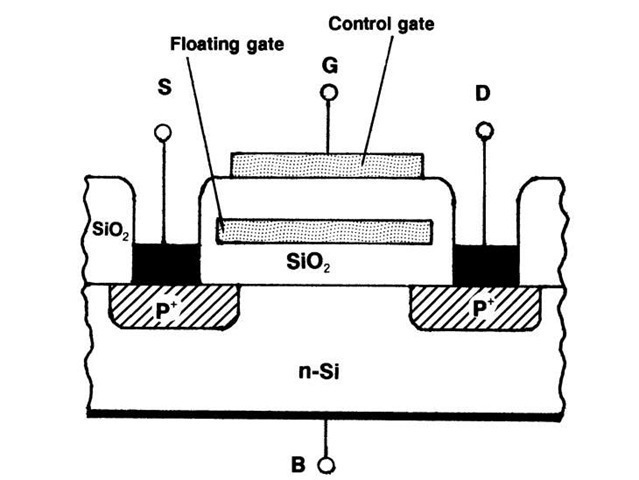

As células de armazenamento em uma EPROM são transistor MOS com porta de sílicio sem conexão(flutuante). No estado normal, o transistor está desligado e a célula armazena 1 lógico.

O transistor pode ser ligado aplicando um pulso de tensão que injeta elétrons de alta energia na região da porta. Estes elétrons ficam presos, pois não há caminho de fuga. A Fig.27 mostra uma célula de uma EPROM.

Uma EPROM pode ser programada pelo usuário e também pode ser apagada e reprogramada quantas vezes desejar. O processo de programar uma EPROM consiste em aplicar tensões especiais (10 a 24V) nos pinos apropriados, durante um certo tempo(50ms por locação).

Fig.28 - EPROMs

Uma EPROM pode ser apagada se for exposta a luz ultravioleta, que produzirá uma corrente da porta flutuante para o substrato, removendo as cargas e desligando o transistor, e restaurando o 1 lógico. Este processo deve gastar entre 15 e 20 minutos, dependendo da memória e intensidade de luz, e apagará toda a memória.

Tempo de acesso rápido com velocidade de até 45 ns

Baixo consumo de energia: corrente de `standby` CMOS igual a 20 μA

Pinagem padrão JEDEC

Fonte de alimentação simples +5 V

Tolerância da fonte de alimentação padrão ±10%

Programação 100% tempo típico de 1 segundo, algoritmo Flashrite™

Proteção latch-up para 100 mA de –1 V + 1 V CC

Alta imunidade a ruído

Interface simples: compatibilidade de entrada/saída CMOS e TTL

Encapsulamento DIP padrão de 28 pinos, PDIP e PLCC de 32 pinos

|

As memórias EEPROMs(E2PROMs) têm a mesma estrutura de porta flutuante que as EPROMs, mas com o acréscimo de uma região com uma fina camada de óxido sobre o dreno do transistor MOSFET da célula de memória.

Fig.31 - Célula de bit EEPROM

Esta modificação produz a característica mais importante das EEPROMs: são apagáveis eletricamente.

Uma alta tensão(21 Volts) entre o dreno e a porta do MOSFET produz uma carga induzida na porta flutuante, que permanece mesmo retirando a tensão de alimentação. Ligando o transistor, armazenando 0 lógico.

Uma tensão reversa de mesmo valor remove as cargas da porta flutuante e apaga a célula de memória. Desligando o transistor, armazenando 1 lógico.

Uma vez que o transporte de cargas precisa de pequenas correntes, apagar e programar uma EEPROM pode ser realizado sem retirar a memória do circuito.

Outra característica das EEPROMs é a possibilidade de programar e apagar eletricamente bytes individuais da matriz da memória. Isto torna muito mais fácil modificar os dados de uma EEPROM. É muito mais rápida a programação de uma EEPROM pois o tempo de programar uma posição de memória é 5ms.

As EEPROMs mais modernas têm internamente os circuitos de suporte para gerar a tensão de programação, controlar a temporização e sequência das operações de programação da memória, o que torna mais simples usar as EEPROMs.

A possibilidade de apagar bytes e o alto nível de integração das EEPROMs apresentam duas desvantagens: densidade e custo.

A complexidade da célula de memória e o circuito de suporte de uma EEPROM reduz a capacidade de bit por milímetro quadrado da pastilha de sílicio, aproximadamente duas vezes a área de uma EPROM.

Tempo de acesso rápido: 90ns(VCC = 5 V) ou 120ns(VCC = 3 V)

Tensão de alimentação: 4,5 V a 5,5 V, e 2,7 V a 3,6 V

Baixo consumo de energia

Escrita rápidas: BYTE e PAGE WRITE(até 64 bytes), 1ms em VCC=4,5V; 3ms em VCC=4,5V; 5ms em VCC=2,7V

Detecção e monitoramento de gravação aprimorados: saída de dreno aberto pronta/ocupada, varredura de dados, bit de chaveamento, status do temporizador de carregamento da página

Encapsulamento aprovado pela JEDEC

Proteção de dados por software

100.000 ciclos de apagamento/gravação (mínimo)

Retenção de dados (mínimo): 10 a 40 anos

|

|

|

EEPROM M28C64: descrição dos sinais

Endereços (A0-A12). As entradas de endereço são usado para selecionar um byte da matriz de memória durante uma operação de leitura ou gravação.

Entrada/saída de dados (DQ0-DQ7). O conteúdo dos dados byte são gravados ou lidos na matriz de memória através dos pinos de E/S de dados.

Habilitação de chip (E'). A entrada de habilitação do chip deve ser mantido baixo para permitir operações de leitura e gravação. Quando Chip Enable é alto, o consumo de energia é reduzido.

Habilitação de saída (G'). Controla os buffers de saída de dados e é usado para iniciar operação de leitura.

Habilitação de escrita (W'). Controle de entrada Write Enable controla se o local endereçado deve ser lido, ou escrito.

Pronto/Ocupado (RB'). Ready/Busy' é uma saída dreno aberto que pode ser usada para detectar o fim do ciclo de gravação interno.

A tabela da Fig.33 resume os quatros modos de operação da EEPROM M28C64 e os níveis de sinais necessários.

Fig.33 - Modos de operação

|

|

|

Questões para Revisão Resolva algumas questões sobre o assunto de tecnologias de memórias MROM, PROM, EPROM, EEPROM . |

Atualizada em