Tabela do Conteúdo da ROM:  Fig.6 |

Equações do decodificador da ROM:

Fig.7-14 |

Equações do codificador da ROM:

Fig.15-18 |

|

||||||||||||||||||||||

| Circuito Lógico da ROM | |||||||||||||||||||||||||

O conteúdo de uma ROM com 8-palavras e 4-bits por palavras é mostrado na Fig.6. A tabela verdade para memória indica que a memória é um conversor de código de entrada(endereços A2A1A0) para outro código de saída(dados D3D2D1D0), isto é, um circuito decodificador em cascata com um circuito codificador. |

Fig.19 |

||||||||||||||||||||||||

| O codificador de uma ROM pode ser implementado empregando uma matriz de diodos, em lugar de portas OR, desde que uma matriz de diodos realiza uma função OR. A Fig.20 mostra o circuito de duas portas OR com diodos: a primeira realiza Z=A+B e a segunda, a operação OR para qualquer número de variáveis de entrada. |

|

|||

Fig.20 |

||||

A Fig.21 abaixo mostra o codificador da ROM 8 X 4-palavrasXbits.

|

|

||

|

|

||

Fig.21 |

|

||

Memórias MROM(MASK ROM - ROM de MÁSCARA)

As memórias MROM têm suas locações de armazenamento programadas pelo fabricante de acordo com as especificações do cliente. As maiores desvantagens da MROM é que não pode ser reprogramada e só é econômica em grandes quantidades.

Fig.23

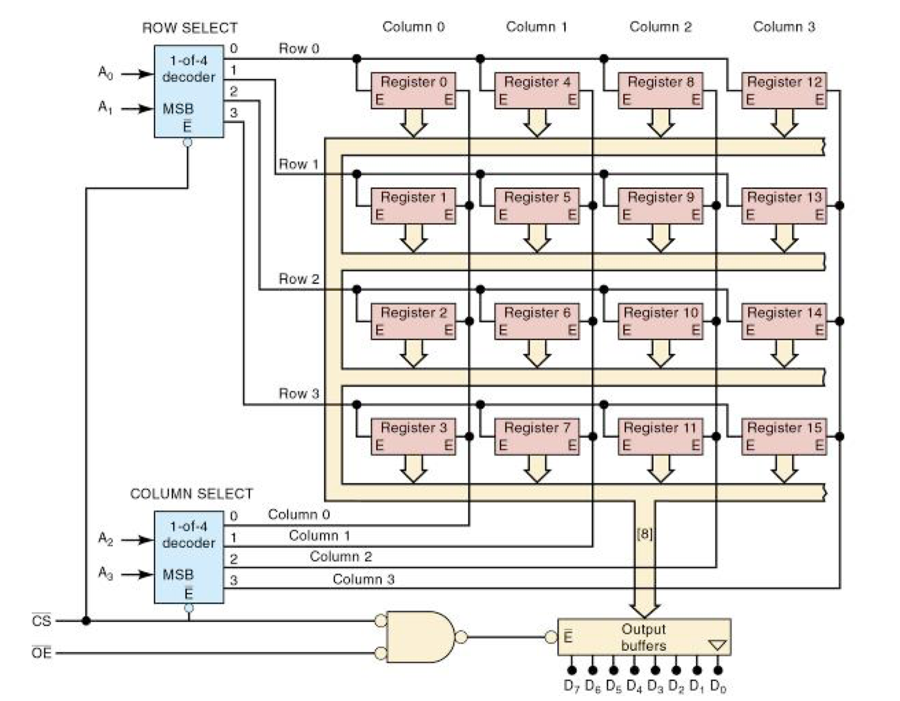

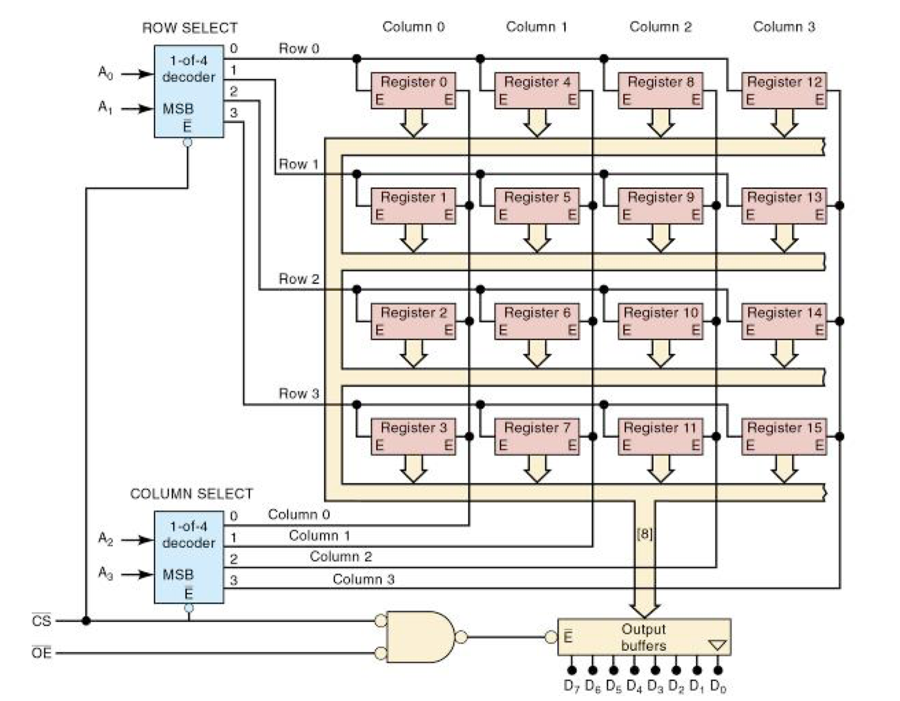

Arquitetura de ROM 16X8 PalavrasXBits

Arquitetura da ROM 16X8 palavrasXbits

Fig.23

Arquitetura de ROM 16X8 PalavrasXBits

Arquitetura da ROM 16X8 palavrasXbits

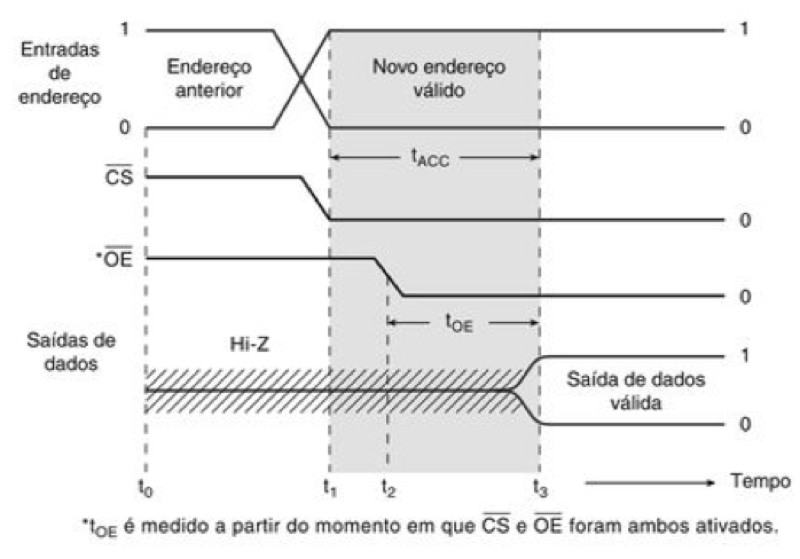

No tempo t0, as entradas de endereços estão em níveis determinados, ALTO ou BAIXO e os sinais de habilitação chip select e output enable estão ALTOS, então as saídas de dados ficam em ALTA IMPEDANCIA(TRI-STATE).

Antes de t1, as entradas de endereços estão mu8dando para uma nova operação de leitura. em t1, o endereço é válido e chip select é ativado, BAIXO.

Em t2, chip select e output enable estão BAIXOS, habilitando os buffers de saída.

Em t3, as saídas passam de ALTA IMPEDANCIA para dados válidos armazenados no endereço de entrada.

O tempo de acesso tacc é igual ao tempo entre os instantes t1, quando o novo endereço é válido, e o instante t3, quando os dados de saída são válidos

| Diagrama de blocos e funções dos pinos |

|

||||

|

|

|

|||

Fig.24 |

|

||||

| Tempo de Habilitação do Circuito | |

| Tempo de Habilitação da Saída | |

| Tempo de Acesso após Endereço | |

| Tempo de Manutenção da Saída | |

| Tempo do Ciclo de Leitura |

Fig.25

OTP PROM TMS27PC256

A série TMS27PC256 são memórias de apenas leitura programáveis eletricamente (PROM) somente uma vez(OTP) organizadas como 32768 X 8- palavrasXbit.

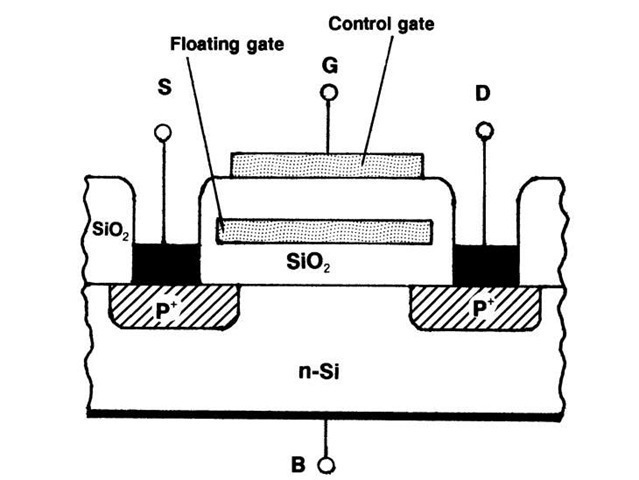

As células de armazenamento em uma EPROM são transistor MOS com porta de sílicio sem conexão(flutuante). No estado normal, o transistor está desligado e a célula armazena 1 lógico. O transistor pode ser ligado aplicando um pulso de tensão que injeta elétrons de alta energia na região da porta. Estes elétrons ficam presos, pois não há caminho de fuga. A Fig.27 mostra uma célula de uma EPROM.

Uma EPROM pode ser programada pelo usuário e também pode ser apagada e reprogramada quantas vezes desejar.O processo de programar uma EPROM consiste em aplicar tensões especiais (10 a 24V) nos pinos apropriados, durante um certo tempo(50ms por locação).

Fig.28

Uma EPROM pode ser apagada se for exposta a luz ultravioleta, que produzirá uma corrente da porta flutuante para o substrato, removendo as cargas e desligando o transistor, e restaurando o 1 lógico. Este processo deve gastar entre 15 e 20 minutos, dependendo da memória e intensidade de luz, e apagará toda a memória.

|

As memórias EEPROMs(E2PROMs) têm a mesma estrutura de porta flutuante que as EPROMs, mas com o acréscimo de uma região com uma fina camada de óxido sobre o dreno do transistor MOSFET da célula de memória. Esta modificação produz a característica mais importante das EEPROMs: são apagáveis eletricamente. Uma alta tensão(21 Volts) entre o dreno e a porta do MOSFET produz uma carga induzida na porta flutuante, que permanece mesmo retirando a tensão de alimentação. Uma tensão reversa de mesmo valor remove as cargas da porta flutuante e apaga a célula de memória. Uma vez que o transporte de cargas precisa de pequenas correntes, apagar e programar uma EEPROM pode ser realizado sem retirar a memória do circuito.

Fig.31 - Célula de bit EEPROM

Outra característica das EEPROMs é a possibilidade de programar e apagar eletricamente bytes individuais da matriz da memória.Isto torna muito mais fácil modificar os dados de uma EEPROM. É muito mais rápida a programação de uma EEPROM pois o tempo de programar uma posição de memória é 5ms.

As EEPROMs mais modernas têm internamente os circuitos de suporte para gerar a tensão de programação, controlar a temporização e seqüência das operações de programação da memória, o que torna mais simples usar as EEPROMs. A possibilidade de apagar bytes e o alto nível de integração das EEPROMs apresentam duas desvantagens: densidade e custo. A complexidade da célula de memória e o circuito de suporte de uma EEPROM reduz a capacidade de bit por milímetro quadrado da pastilha de sílicio, aproximadamente duas vezes a área de uma EPROM.

|

|

|

A tabela da Fig.33 resume os quatros modos de operação da EEPROM M28C64 e os níveis de sinais necessários.

Fig.33

|

| Questões para Revisão Resolva algumas questões sobre o assunto de tecnologias de memórias ROMs. |

|||

|

|

|

Questões para Revisão Resolva algumas questões sobre o assunto de tecnologias de memórias MROM, PROM, EPROM, EEPROM . |

|

Atualizada em