Memórias DRAMs armazenam os dados enquanto a tensão de alimentação estiver aplicada ao circuito integrado. A célula de memória é um capacitor de alguns picofarads.

Tecnologia de DRAMs: MOS

Características

|

Desvantagens

|

A densidade típica de uma DRAM é quatro vezes a densidade de uma SRAM.

Enquanto o consumo de potência de uma DRAM é um sexto a metade do consumo de uma SRAM.

O custo de armazenamento por bit de uma DRAM é um quinto a um quarto de uma SRAM.

As memórias RAM dinâmicas armazenam os 1s e 0s como cargas em pequenos capacitores CMOS (alguns picofarads).

Como estes capacitores tendem a perder cargas com decorrer do tempo, as DRAMs precisam periodicamente recarregar as células de memórias(capacitores).

Esta operação é denominada refrescamento(refreshing) de uma DRAM.

O período de refrescamento típico para as DRAMs atuais varia de 2 a 8ms.

A célula de memória de uma DRAM é constituída por um capacitor e circuitos associados para prover os meios necessários para o refrescamento da célula de memória.

A Fig.5 mostra a representação da célula de memória de uma DRAM.

As chaves SW1 a SW4 são MOSFET que são controladas pelas várias saídas dos decodificadores de endereços e sinais de leitura/escrita.

| Operação de Escrita: | SW1, SW2 ON SW3, SW4 OFF |

| Operação de Leitura: | SW2, SW3, SW4 ON SW1 OFF |

O Amplificador Sensor(Sense Amplifier) compara a tensão da célula com uma tensão de referência para determinar se o valor lógico armazenado é 0 ou 1, fornece um valor de tensão nominal na saída de dados.

Esta tensão de saída é ligada à célula através das chaves SW2 e SW4, e refresca a tensão do capacitor, carregando-o ou descarregando-o.

Ou seja, o dado armazenado é refrescado cada vez que a célula é lida.

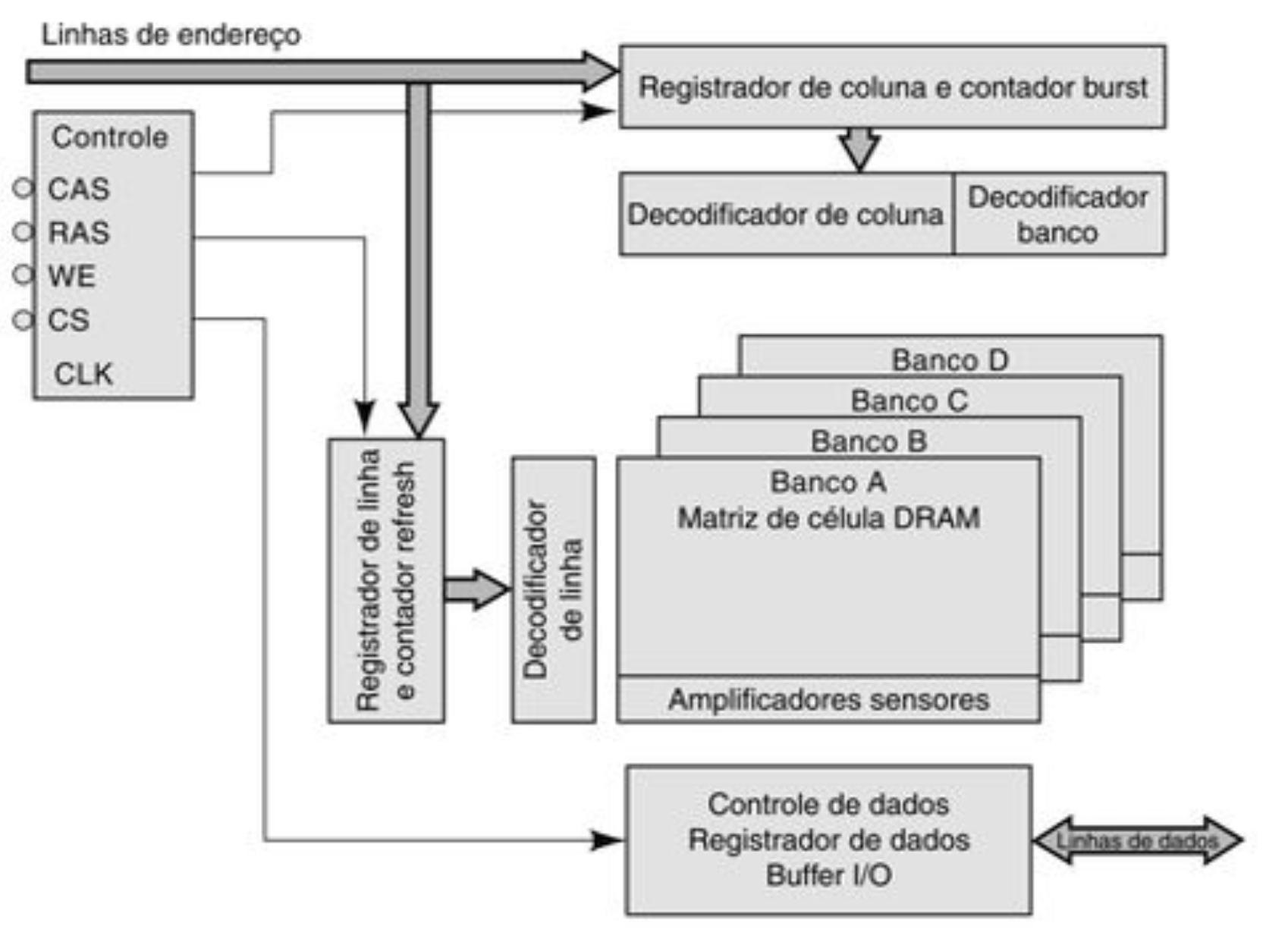

A arquitetura interna de uma DRAM com capacidade igual a 16K x 1 palavrasXbits é mostrada na Fig.6, onde 16.384 células estão arranjadas em uma matriz 128X128, onde cada célula ocupa uma posição única em uma linha e em uma coluna dentro da matriz.

São necessários 14 bits de endereços A13 até A0 para selecionar uma célula.

Os endereços mais baixos A0 até A6 selecionam a linha.

Os endereços mais altos A7 até A13 selecionam a coluna.

As células de memória estão dispostas em vários bancos de matrizes retangulares. Uma única linha (para cada banco) é selecionada pelo decodificador de linha. O endereço da coluna é decodificado e usado para selecionar um dos bancos e selecionar uma coluna para cada bit na palavra de dados.

Se a DRAM usar uma palavra de dados de oito bits, um determinado endereço de coluna habilitaria as oito colunas que compõem esse local de memória de oito bits.

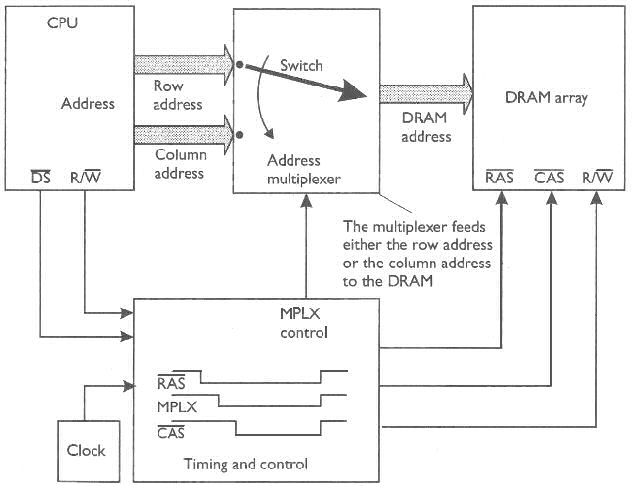

Multiplexação de Endereços em DRAMs

As DRAMs são fabricadas em chips de alta capacidade de armazenamento, requerendo um grande número de bits de endereços.

Para reduzir o número de pinos de endereços de uma DRAM, os fabricantes empregam a multiplexação de endereços, onde cada pino de entrada pode acomodar dois bits de endereço diferentes.

A temporização das operações de leitura e escrita para uma memória DRAM são mais complexas que as operações de uma SRAM.

A multiplexação do barramento de endereços aumenta a complexidade da interface entre a DRAM e a CPU.

A Fig.8 mostra a lógica necessária para controlar uma memória dinâmica .

O bloco de temporização e contrôle(Timing and Control) deve executar a multiplexação de endereços e gerar os sinais CAS' e RAS' ativos BAIXOS necessários.

| Row Address Strobe | Gatilha o registrador de endereços de linha | |

| Column Address Strobe | Gatilha o registrador de endereços de coluna |

Os bits de endereços são aplicados na DRAM em duas etapas através do uso dos sinais ![]() e

e ![]() , ativos BAIXOS, conforme mostra a Fig.9 abaixo.

, ativos BAIXOS, conforme mostra a Fig.9 abaixo.

A DRAM não possui uma entrada de seleciona circuito(CS-Chip Select).

Os sinais ![]() e

e ![]() realizam a função de seleciona circuito, desde que os dois sinais devem ser BAIXOS para os decodificadores selecionarem uma célula para leitura ou escrita.

realizam a função de seleciona circuito, desde que os dois sinais devem ser BAIXOS para os decodificadores selecionarem uma célula para leitura ou escrita.

| Questões para Revisão Resolva algumas questões sobre o assunto de Memórias DRAMs. |

||

Atualizada em