Memórias de Acesso Aleatório(Random Access Memories - RAMs)

As memórias RAMs são empregadas para armazenamento temporário de programas e dados.

Principal vantagem: operações de leitura/escrita com iguais facilidades.

Principal desvantagem: volatilidade.

Arquitetura das Memórias RAMs

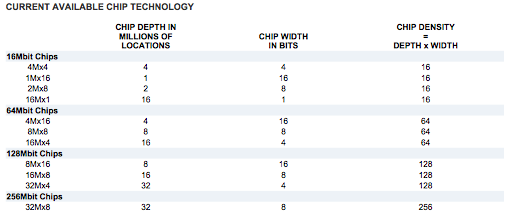

RAMs são encontradas nas capacidade: 1K, 4K, 8K, 16K, 128K, 256K, 1M, 2M, 4M, 8M, 16M, 32M, 64M, 128M, 256M, 512M, 1G, 2G, 4G, 8G, 16G, 32Gb, 64Gb e 128Gb.

RAMs apresentam palavras de 1, 4, 8, 16, 32 bits.

RAM 64x4-palavrasXbits

Para economizar pinos na periferia do CI, as memórias RAMs combinam o pino de entrada/saída de dados em um único pino.

|

|

|

Fig.1 |

|

|

| Operação de Leitura: | Operação Seleciona Circuito: |

|

|

|

||

| Operação de Escrita: |

|

|

|

|

||

Memórias SRAMs armazenam os dados enquanto a tensão de alimentação estiver aplicada ao circuito integrado. A célula de memória pode ser um latch ou flip-flop.

Tecnologias de SRAMs: Bipolar, MOS e BiCMOS.

Tecnologias mais usuais: NMOS e CMOS.

As SRAMs bipolares são mais rápidas, enquanto as MOS apresentam menor custo e maior capacidade.

Temporização de SRAM

A nomenclatura dos parâmetros varia de fabricante para fabricante.

Ciclo de Leitura

|

||||||||||||

Fig.2 |

||||||||||||

|

Ciclo de Escrita

|

|

|

|||||||||||||||

Fig.3 |

|

||||||||||||||||

Características

JEDEC, Joint Electron Device Engineering Council, organização que fornece os padrões para os fabricantes de CIs.

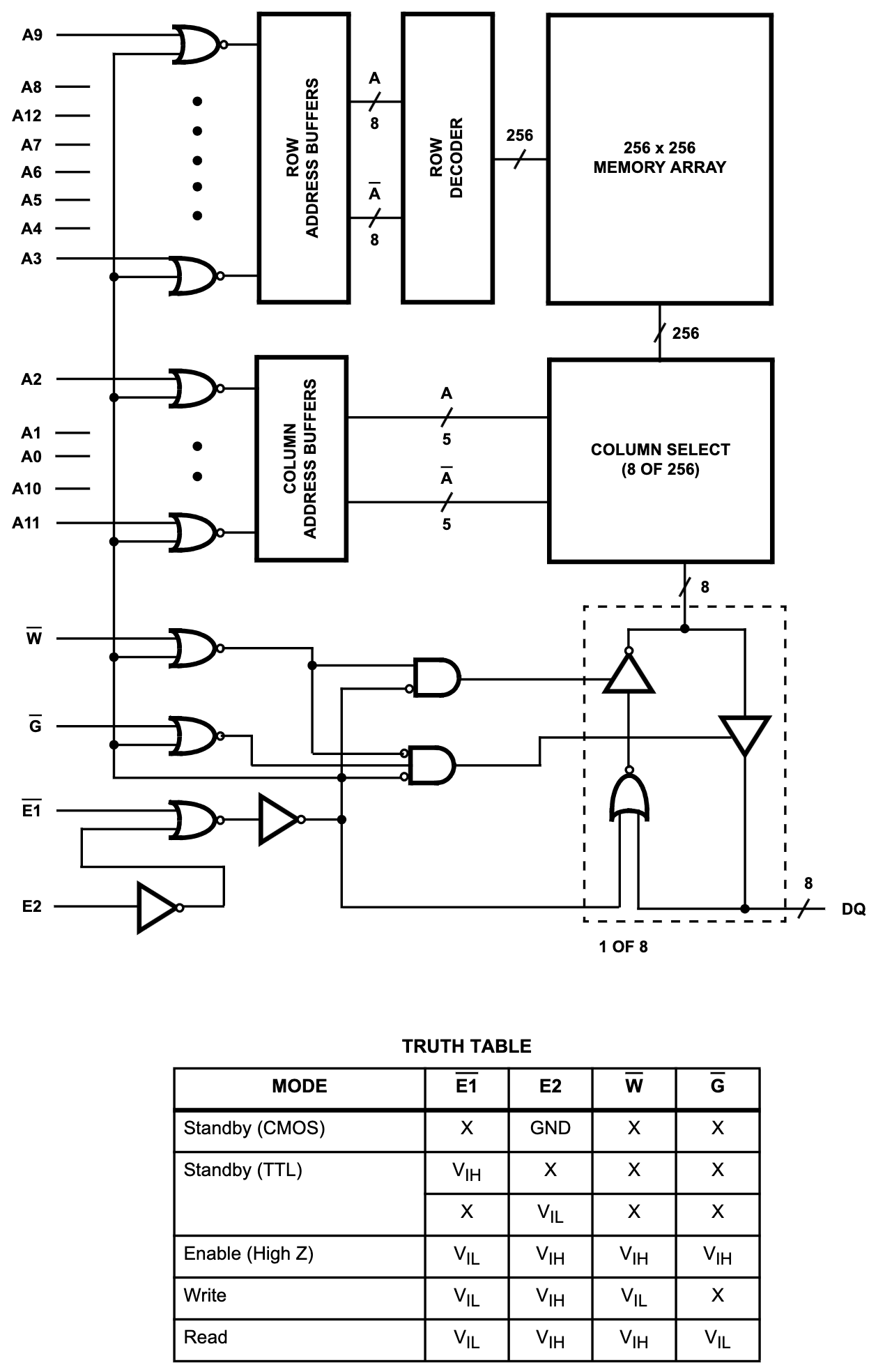

Fig.4 - SRAM HM-65642 - RENESAS - Pinagem

Fig.4a - SRAM HM-65642 - RENESAS - Diagrama Funcional.Tabela Verdade

Características

| Questões para Revisão Resolva algumas questões sobre o assunto Tecnologia e Estrutura de Memórias de Acesso Aleatório. |

||

|

||

Atualizada em