Microprogramação é uma técnica adicional de realizar controle de um processador(computador).Os sinais de comando que são aplicados aos terminais de controle dos registradores, ULA e memórias, para realizar as microoperações, são disponíveis como palavras de dados de uma memória.

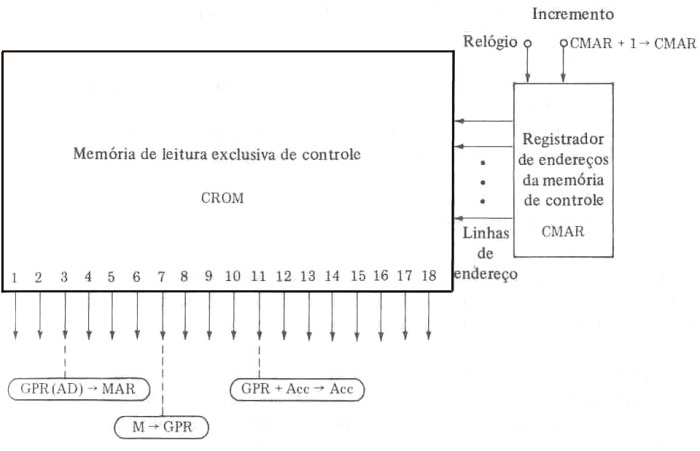

Memória ROM de controle é a memória que contém os dados onde cada bit da palavra corresponde a um terminal de entrada de controle.Vamos supor um computador com 18 terminais de controle como visto anteriormente. Então, a ROM de controle tem palavras de 18-bits, um bit para cada terminal de entrada de controle.

|

Então, faz-se corresponder o pino 3 da ROM de controle ao terminal de entrada de controle GPR(AD)->MAR, o pino 7 ao terminal M->GPR, o pino 11 ao terminal GRP+Acc->Acc, arbitrariamente.Caso a instrução a ser realizada seja ADDI,end, então o conteúdo da ROM de controle(CROM - Control ROM) deve ter escrito em cinco posições sucessivas da memória o conteúdo seguinte:

|

Em cada ciclo do relógio apenas uma microoperação é realizada e em cada palavra da CROM somente um bit está no nível lógico 1.Quando várias microoperações precisam ser realizadas no mesmo ciclo de relógio, um número correspondente de bits 1 estará escrito na palavra da CROM.

Palavras de Controle ou Micropalavra é o conteúdo da posição da memória de controle, que através da leitura sucessiva, executa uma seqüência de microoperações armazenadas na memória de controle, cujo resultado final é a execução de uma operação.

Microinstrução - palavra ne memória CROM que identificam as microoperações.

Processador Microprogramado - opera com microinstruções armazenadas em memória ROM de controle.

Um computador ou processador microprogramado tem dois tipos de memória;

Desvio(Branch) do Microprograma

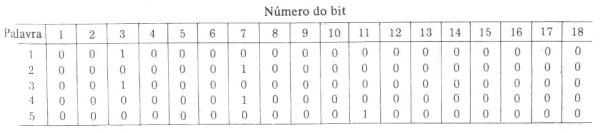

A CROM acima só permite que as microinstruções sejam acessadas na ordem como estão escritas na memória. Um arranjo que permite um desvio(branch) ou salto(jump) para uma posição qualquer da memória é mostrado na figura abaixo.

|

Observe que o tamanho da micropalavra é formado por N+M+1 bits, onde cada parcela tem uma função específica. a palavra da CROM contém um endereço(M-bits), uma microinstrução(N-bits) e um controle(1-bit).

N : número de bits de comando para as N-entradas de terminais de controle dos registradores do computador;

M : número de bits de endereço para onde deve ocorrer o salto ou desvio, sob comando;

1 : bit que comanda o salto ou desvio; bit de controle de carga inativo(0), então a entrada de incremento está ativa(1) e o registrador de endereços é incrementado a cada ciclo do relógio; se o bit de controle de carga está ativo(1), então incremento está inativo(0) e o endereço de desvio será carregado (endereço de M-bits para onde haverá o desvio ou salto).

Desvio Condicional

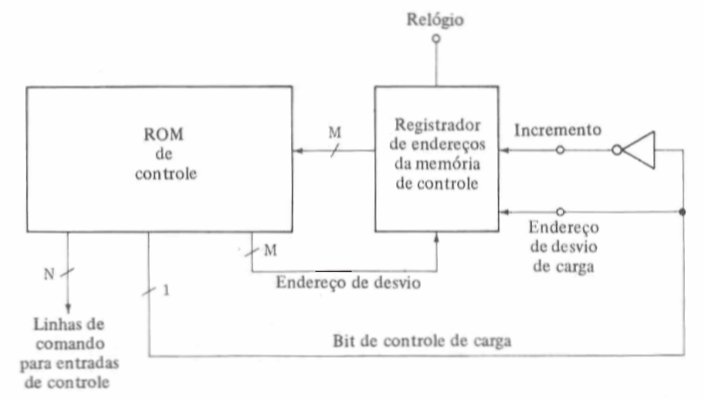

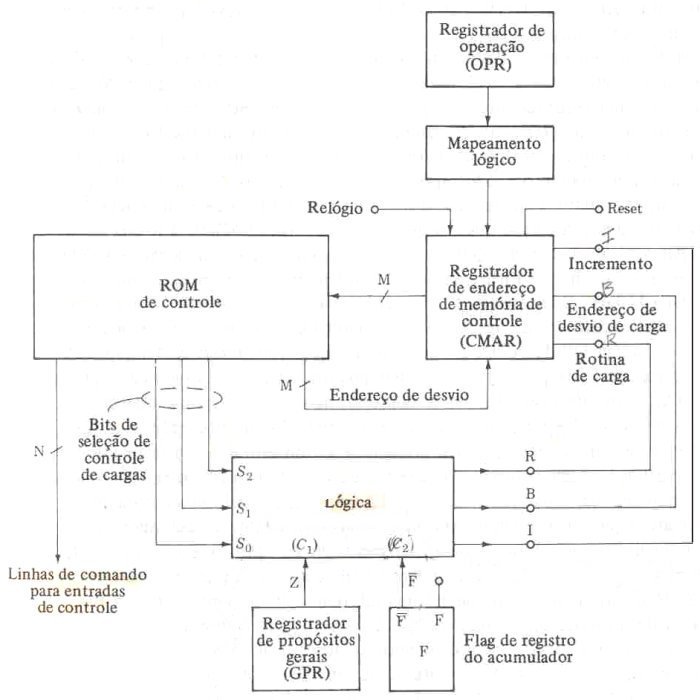

Para prover o controlador(CROM e CMAR) de flexibilidade para seguir uma seqüência ou outra dependendo dos resultados internos do processamento, a arquitetura acima é modificada para fornecer estes recursos, conforme mostrado abaixo.

|

S1, S0 : bits de seleção de controle de carga.

C1, C2 : bits de estado, indicam alguma condição interna e permitem o controlador seguir uma seqüência ou outra.

B : terminal de controle do CMAR, que carrega o endereço de desvio ou salto.

I : terminal de controle do CMAR, que realiza o incremento do registador.

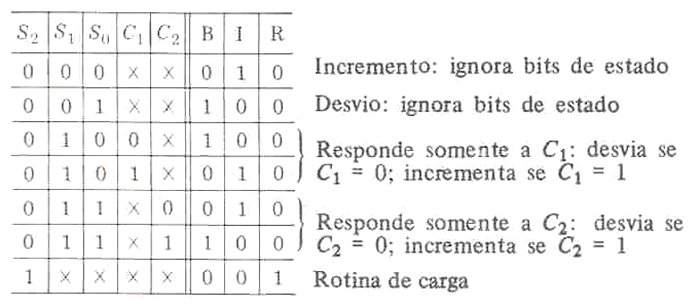

O bloco chamado Lógica tem a tabela verdade mostrada na Fig.4 e de acordo com os valores lógicos das entradas S1, S0, C1 e C2 ativa as linhas de controle B ou I, conforme a tabela verdade, para haver desvio ou incremento.

Bombeamento(Pipelining)

A existência de atrasos associados ao controlador e ao sistema controlado condicionam a velocidade de resposta do controlador.A Fig.4 acima mostra o controlador microprogramado com o bloco lógico Registrador de Bombeamento, que serve para melhorar a velocidade de operação do controlador.

Atrasos sem Registrador de Bombeamento

| Instante de gatilhamento do relógio e início do estabelecimento de novo endereço em CMAR | |

| Tempo necessário para estabelecer um endereço válido na saída de CMAR(M-bits válidos e fixos) | |

| Atraso de propagação da memória de controle CROM | |

| A microinstrução endereçada válida está na saída da memória de controle CROM | |

| Tempo de resposta do sistema controlado(responde às microinstruções e completa as respostas) | |

| Período mínimo permissível do relógio |

O tempo tR é a maior parcela do atraso total, pois deve contemplar a microoperação mais longa(em geral, operação de leitura ou escrita em uma RAM).

Pode-se economizar tempo começando a estabelecer uma nova micropalavra antes do sistema controlado ter concluído sua resposta à micropalavra anterior.Consideremos os tempos e atrasos de propagação envolvidos.

| Tempo do atraso de propagação do bloco lógico desvio/incrementa | |

| Período do relógio | |

| Instante em que nova micropalavra válida está disponível na saída de CROM | |

| Instante em que um bit de controle de carga válido é fornecido para CMAR e ocorre gatilhamento |

Então, com o período de relógio igual a tC = tA + tM + tXnovas micropalavras aparecerão na saída da CROM em sucessão, na taxa do relógio.Se o tempo de resposta do sistema controlado tR fôr menor que o período do relógio tC então o sitema terá tempo adequado para responder a cada microinstrução .O sistema realiza a resposta a uma microinstrução no mesmo tempo que a próxima microoperação está fazendo seu caminho através da lógica de desvio/incrementa e memória de controle CROM. Deve-se esperar um tempo igual a tA + tM para que a saída da CROM se estabilize.

O registrador de bombeamento é acionado pela mesma forma-de-onda de relógio que aciona o registrador de endereços. A transição de relógio que incrementa ou carrega o registrador de endereços é a mesma transição que carrega ao registrador de bombeamento com a micropalavra na saída da CROM.. A resposta do sistema controlado pode começar no instante em que o registrador de bombeamento fôr carregado.Neste instante, pode-se mudar o endereço a fim de fazer aparecer a próxima microinstrução.

Enquanto o sistema controlado estiver completando a resposta, os bits da palavra de saída da CROM podem mudar que não causam problemas porque o sistema está separado da microinstrução variável pelo registrador de bombeamento.

Controlador Microprogramado

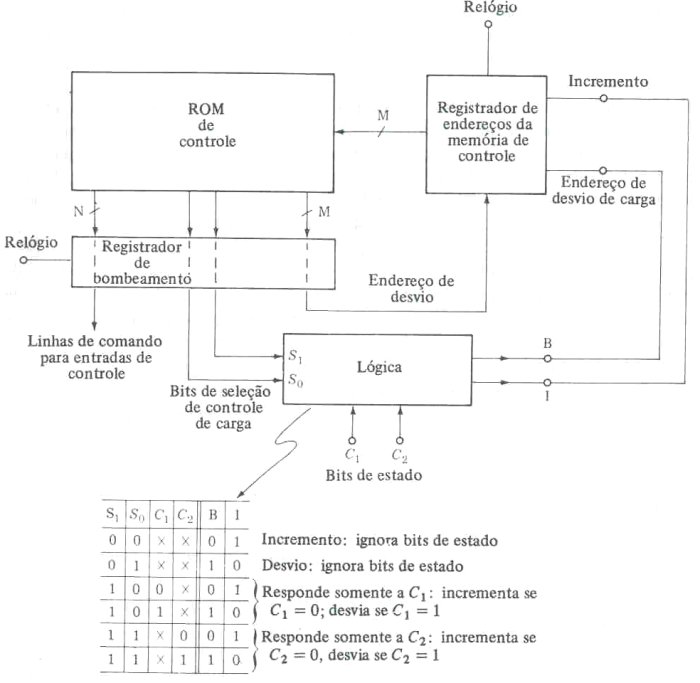

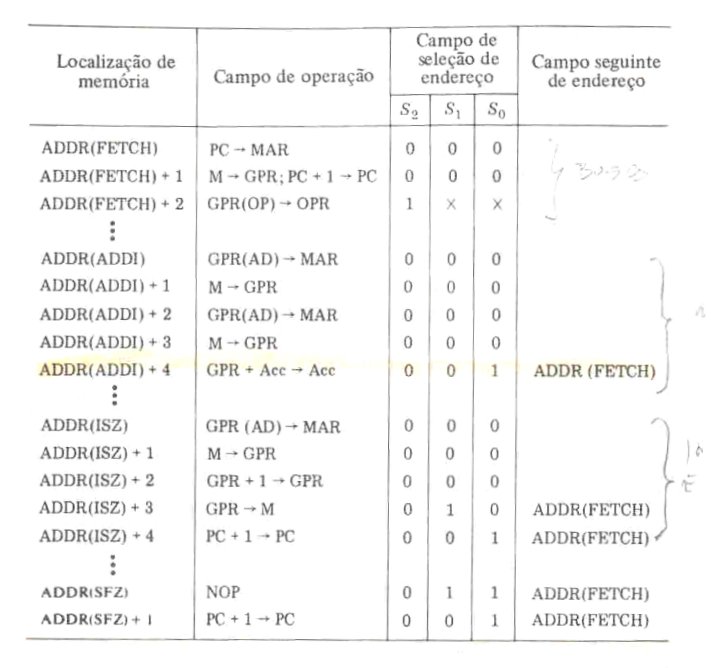

O circuito abaixo mostra a implementação do controlador, para uma arquitetura do computador, realizado como um controlador microprogramado.

|

O bit de condição de desvio C1 é igual ao bit Z do GPR e dá o estado de GPR;

O bit de condiçaõ de desvio C2 é igual ao complemento do bit F e dá o estado do registrador F.

O circuito permite o carregamento no CMAR de um endereço determinado pelo código de operação registrado no registrador de operações.

Rotina de Carga(R): comanda o carregamento no CMAR do endereço determinado pelo OPR e bloco de Mapeamento Lógico.

S2, S1, S0: bits de seleção de controle de carga.

Rotina de Busca(Fetch): seqüência de microoperações escrita na CROM como uma seqüência de micropalavras, que executa as operações necessárias para buscar uma instrução.

ADDR(FETCH): posição da memória de controle CROM onde começa a Rotina de Busca.

Rotina de Executar: seqüência de microoperações que executam uma instrução.

O controlador entra na seqüência através da rotina de busca incrementando CMAR após cada microoperação.No fim da rotina de busca , a operação necessária pela instrução está carregada no registrador de operações(OPR).Então, é necessário que no fim da rotina de busca exista um desvio para o endereço onde começa a rotina de executar da instrução.O endereço onde começa a rotina de executar a instrução é determinado pelo código de operação no registrador de operações(OPR).

Mapeamento: tradução do código de operação OP num endereço que dá partida à rotina de executar da instrução.

Lógica de Mapeamento: bloco combinacional entre o registrador de operações(OPR) e o CMAR, que aceita o código OP como entrada e fornece como saída o endereço que dá partida à rotina de executar da instrução.

O bloco lógico de desvio/incrementa tem a tabela verdade mostrada na figura abaixo:

|

Quando S2=1, então R=1 e o endereço da rotina de executar da instrução especificada pelo registrador de operações será carregado no CMAR.

Conteúdo da ROM de Controle

Os bits que compõem a micropalavra são divididos em três campo:

|

|

Métodos de Endereçamento

Em geral, uma instrução é dividida em duas partes: parte de operação e parte do endereço(do operando).

Modos de endereçamento:

Pushing(Colocação): escrita de uma palavra na pilha

Popping(Extração ou Retirada): leitura de uma palavra na área da pilha

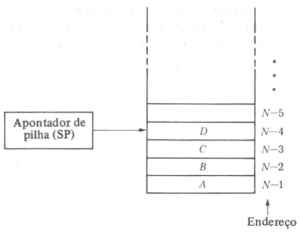

Em geral, uma área de pilha é implementada usando uma área determinada da memória RAM.

Apontador ou Indicador de Pilha(SP): registrador do contador que é incrementado ou decrementado para acessar um endereço da pilha.

O apontador de pilha(SP) contém o endereço que se tem acesso para leitura ou escrita.

|

Os dados são colocados na pilha do endereço maior para o endereço menor: primeiro é colocado A no endereço N-1, em seguida B no endereço N-2, depois C em N-3, e D em N-4. Na leitura ou extração, primeiro retira-se D, depois C, em seguida B e, por último, A.

Escrita na Pilha:

|

A pilha, usada em um sistema microprogramado, permite que uma seqüência de microinstruções acessar outra seqüência de microinstruções de uso frequente.Isto se chama 'aninhamento'(nesting) de seqüências, ou encadeamento de seqüências.

|

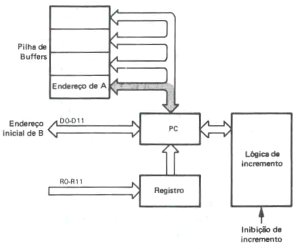

A seqüência a de microoperações chega no ponto de execução onde a seqüência B de microinstruções deve ser acessada . O endereço corrente de A é salvo(armazenado) na pilha e o da seqüência B é enviado. |

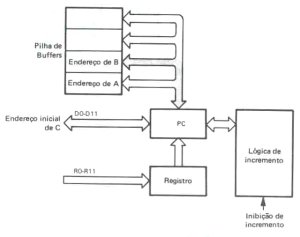

| A seqüência B de microinstruções está no ponto de execução onde a seqüência C de microinstruções deve ser acessada. O endereço corrente da seqüência B é armazenado na pilha e o endereço da seqüência C é enviado. |

|

|

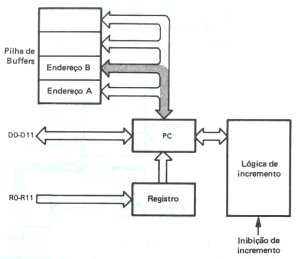

A seqüência C de microinstruções completa sua execução, então o endereço armazenado durante a execução da seqüência B é restaurado no PC. |

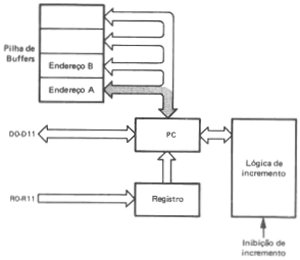

| A seqüência de microinstruções B também completa sua execução, e então o endereço salvo de A é restaurado no PC. |

|

A lógica de endereçamento da unidade de controle para usar a pilha necessita de dois sinais de controle adicionais: um para salvar o conteúdo do PC na pilha(PUSH); o outro irá restaurar o endereço do topo da pilha no PC(POP).

| História do Microprocessador Esta página da Intel mostra a história do processador moderno, como evoluiu desde a arquitetura mais simples até os potentes processadores atuais. É preciso ter o plug-in Adobe Reader instalado. |

Atualizada em