Aluno:_____________________________________________________CPF:______________

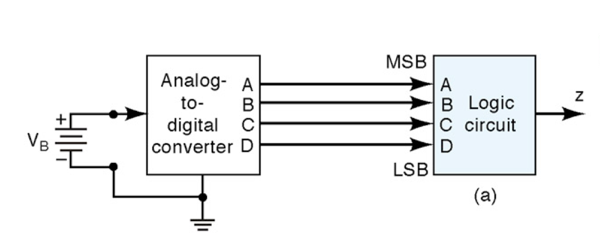

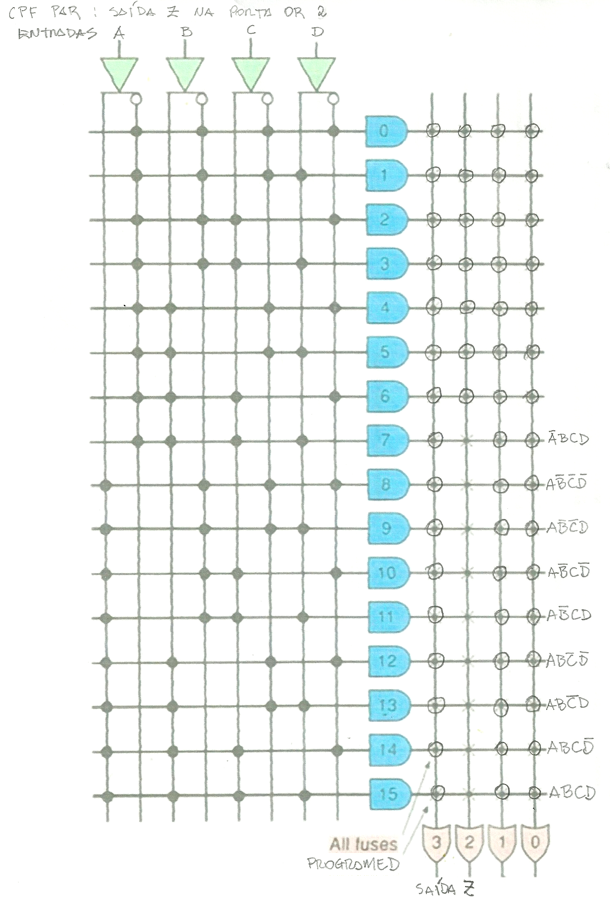

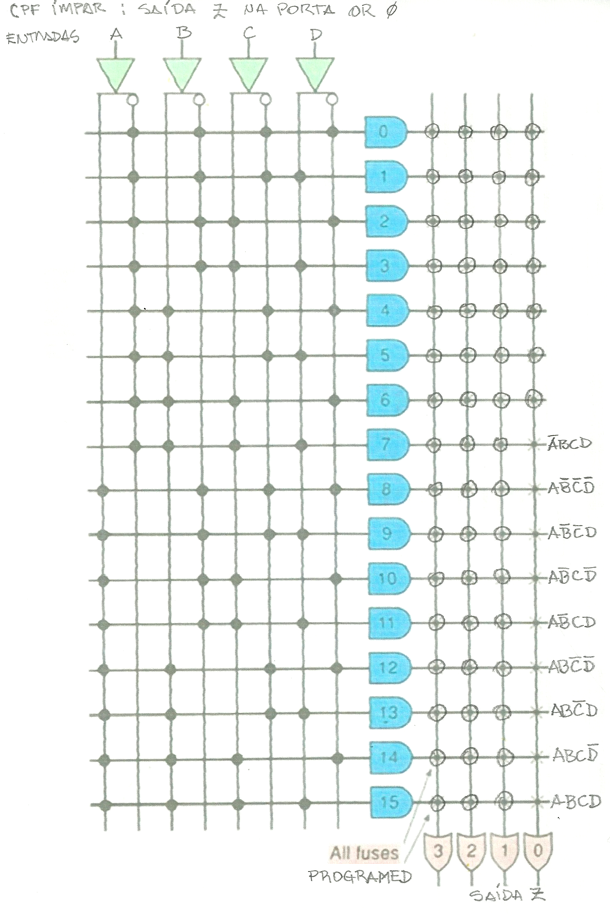

1.O circuito da Fig.1 mostra um conversor analógico-digital monitorando a tensão CC(VB) de uma bateria de 12V. A saída do conversor fornece um número binário de quatro bits ABCD, que corresponde `a tensão da bateria em degraus de 1V, onde A é o dígito mais significativo. As saídas binárias ABCD do conversor são entradas de um circuito lógico que gera uma saída Z que será ALTA para indicar quando a tensão da bateria for maior que 6V. Utilizando o PLD mostrado, programe o circuito lógico detetor da tensão da bateria, considerando as seguintes condições:

(a)Seu CPF é par, então o detetor da tensão da bateria deve indicar a saída Z no pino da porta OR 2;

(b)Seu CPF é ímpar, então o detetor da tensão da bateria deve indicar a saída Z no pino da porta OR 0;

Solução

Valor da questão = 5,0

Cada locação programada correta = 0,32

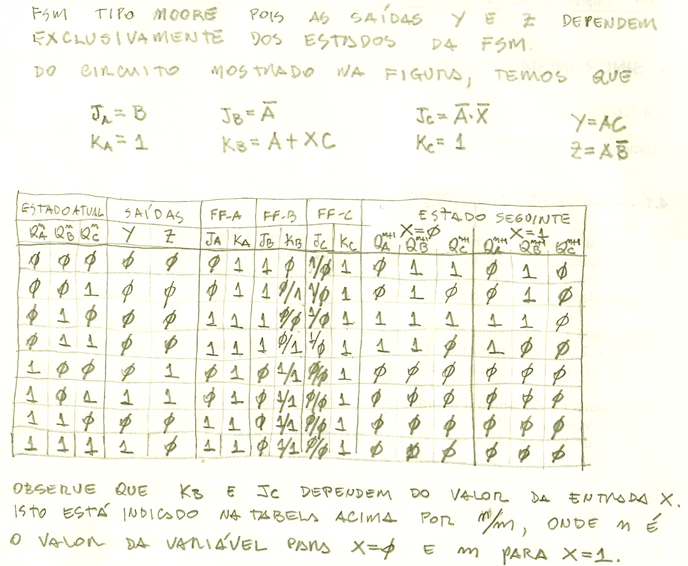

2.O circuito sequencial da FSM mostrado na Fig.2 tem uma entrada X e duas saídas YZ. Considere que o estado inicial da FSM é igual à 000(CPF par) e 111(CPF ímpar) e a sequencia em binário de X é igual `a representação BCD dos tres dígitos mais significativos do CPF. Então, complete o preenchimento da tabela de transição da FMS.

Solução

PS(ABC) |

||||||||||||

YZ |

||||||||||||

X |

||||||||||||

NS(ABC) |

Valor da questão = 5

Cada coluna correta = 0,42

Atualizada em