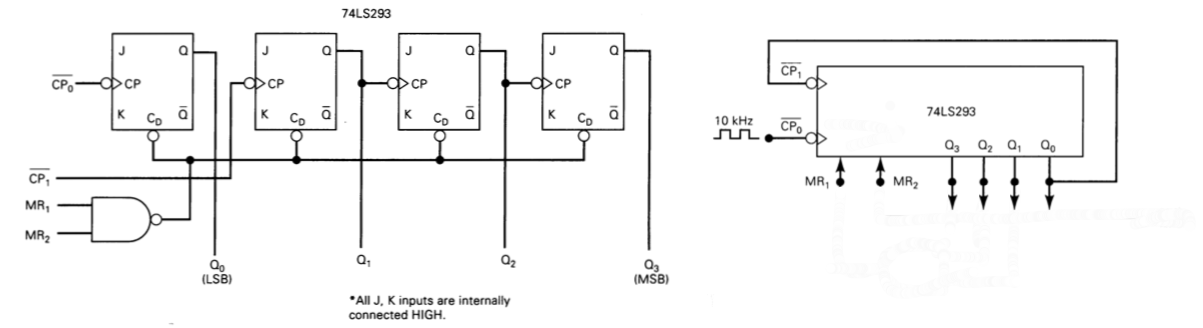

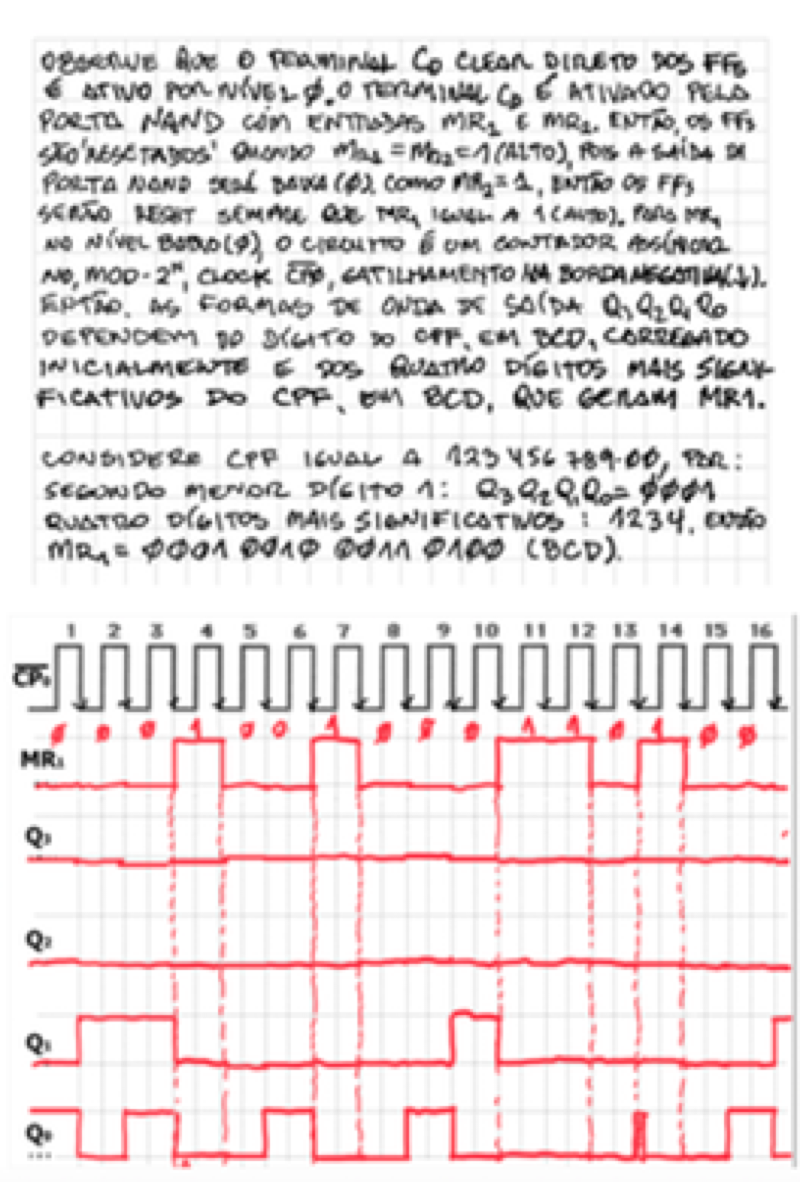

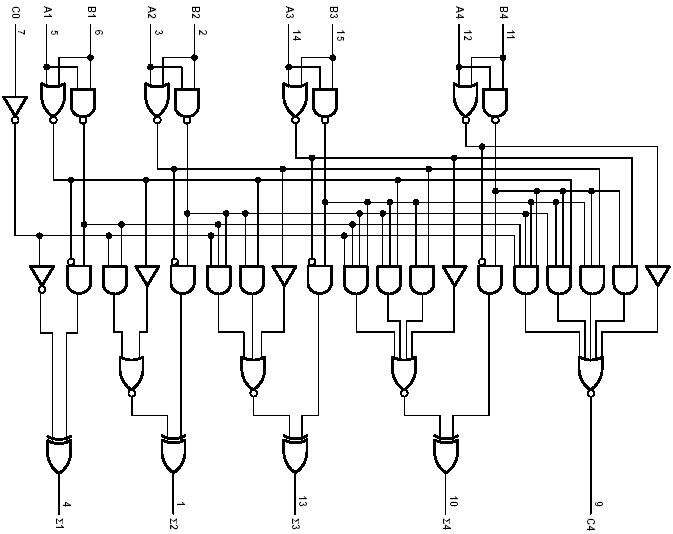

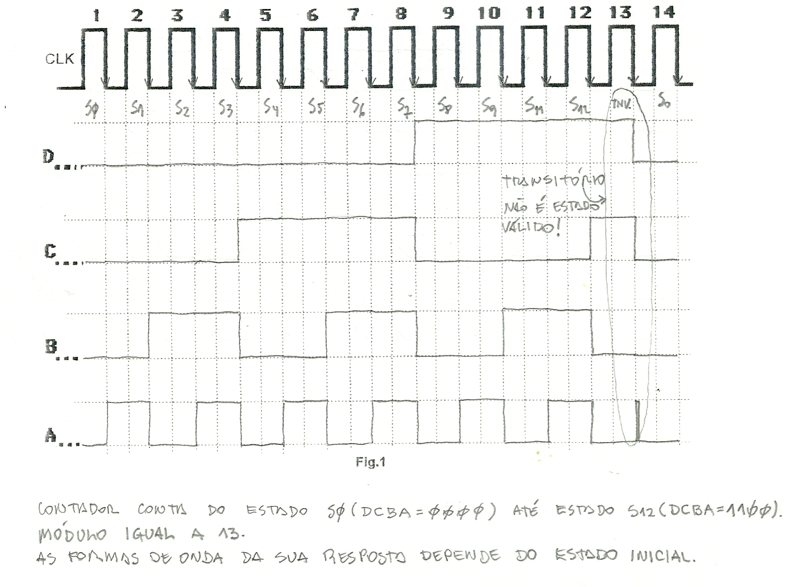

1. A figura abaixo mostra o diagrama lógico de contador assíncrono de quatro bits 74LS293. Analise sua operação, desenhe as formas de onda para cada sinal de saída Q0, Q1, Q2, Q3, e MR1, na configuração mostrada. Use o sinal de clock abaixo e admita que o conteúdo inicial do contador seja igual à representação BCD do segundo menor dígito do seu CPF, se o CPF for par; e igual à representação BCD do segundo maior dígito do CPF, se o CPF for ímpar. Considere MR1 igual à representação BCD dos quatros números mais significativos do CPF e MR2 igual a 1(ALTO).

Solução

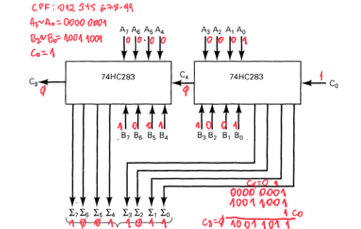

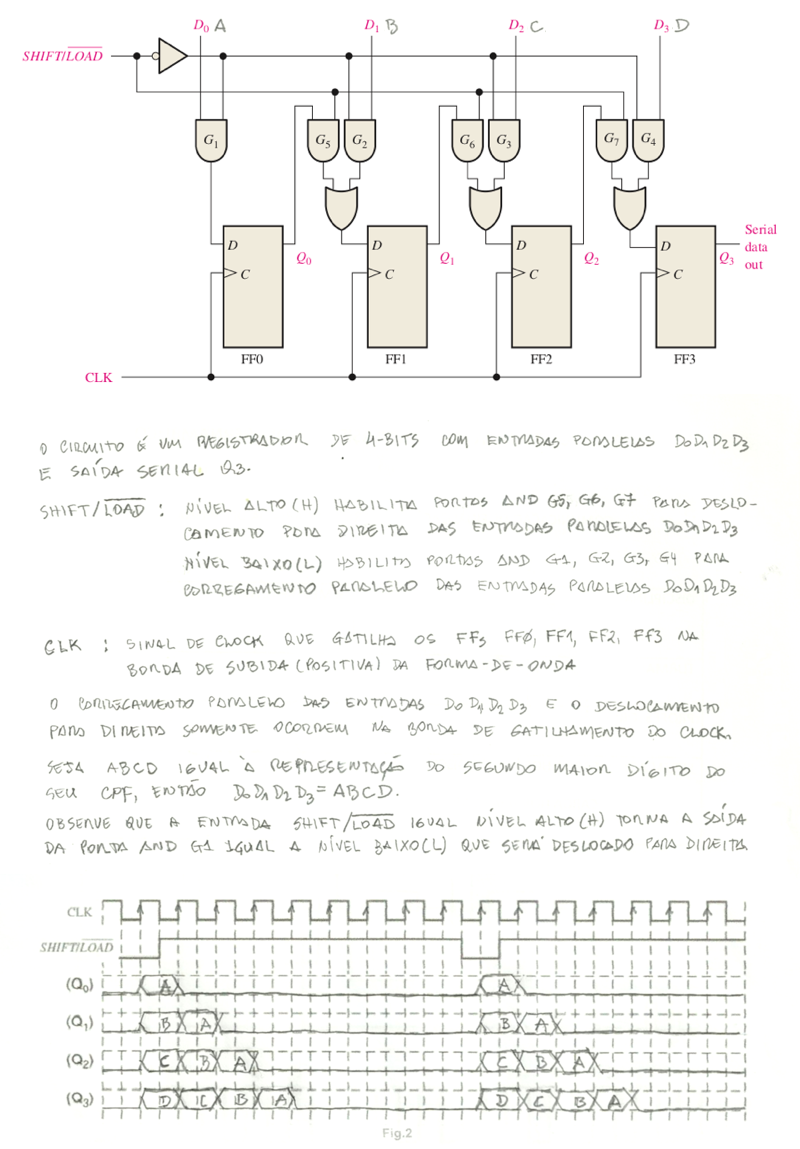

2.Para o somador mostrado na Fig.2, sabendo que A7A6A5A4A3A2A1A0 é igual à representação BCD dos dois dígitos mais significativos do CPF e B7B6B5B4B3B2B1B0 é igual à representação BCD dos dois dígitos menos significativos do CPF, determine as saídas ∑7∑6∑5∑4∑3∑2∑1∑0, C4 e C8. Considere que C0 igual a 1 se seu CPF é ímpar e C0 igual a 0 se seu CPF é par.

Solução

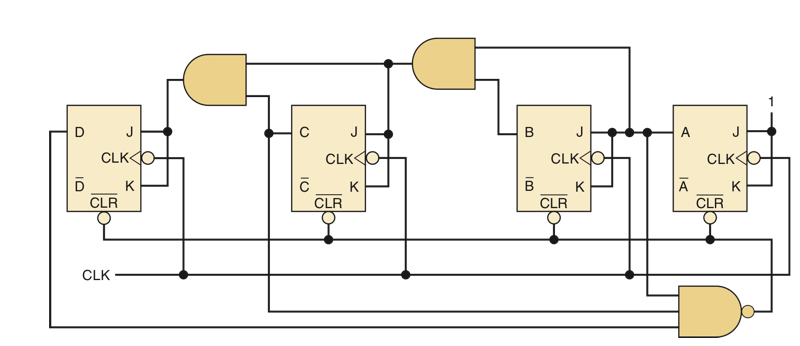

3.A Fig.3 abaixo mostra o circuito lógico do registrador de 4-bits, com clock CLK, entradas D0D1D2D3, e SHIFT/LOAD, com as ligações mostradas. No início, o registrador está RESETADO e com as entradas D0D1D2D3 iguais à representação em BCD do segundo maior número do seu CPF, então responda as questões abaixo.

a) Função da entrada SHIFT/LOAD`= 0 (CPF par) e SHIFT/LOAD`= 1 (CPF ímpar)

b) Desenhe as formas de ondas das saídas Q3Q2Q1Q0 do registrador.

Solução