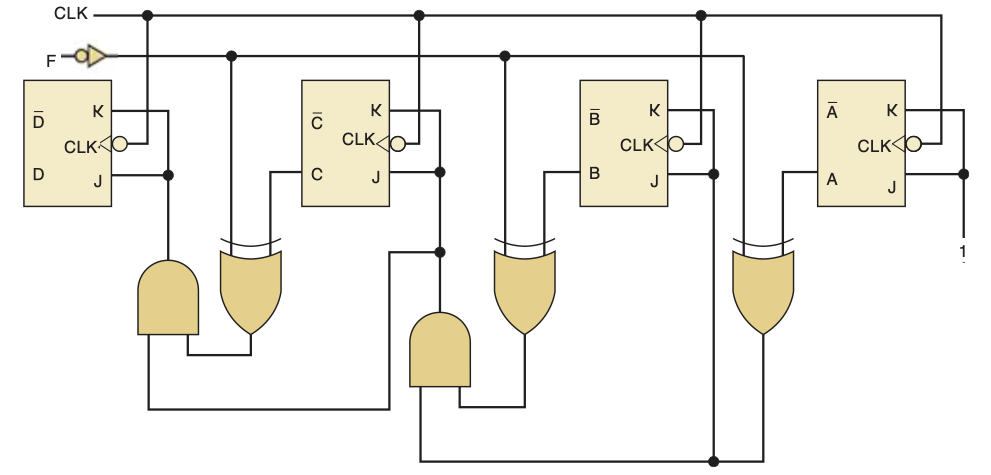

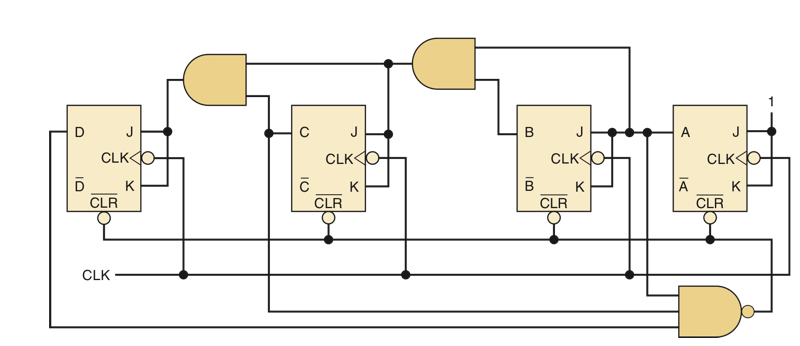

1. Analise o contador síncrono da Fig.1. Considere que inicialmente o contador está com DCBA igual à representação BCD do segundo maior dígito do seu CPF e F está no nível ALTO se seu CPF é ímpar e F está no nível BAIXO se seu CPF é par. Então preencha a tabela com os estados do contador após cada borda do CLK.

Solução

Fig.1

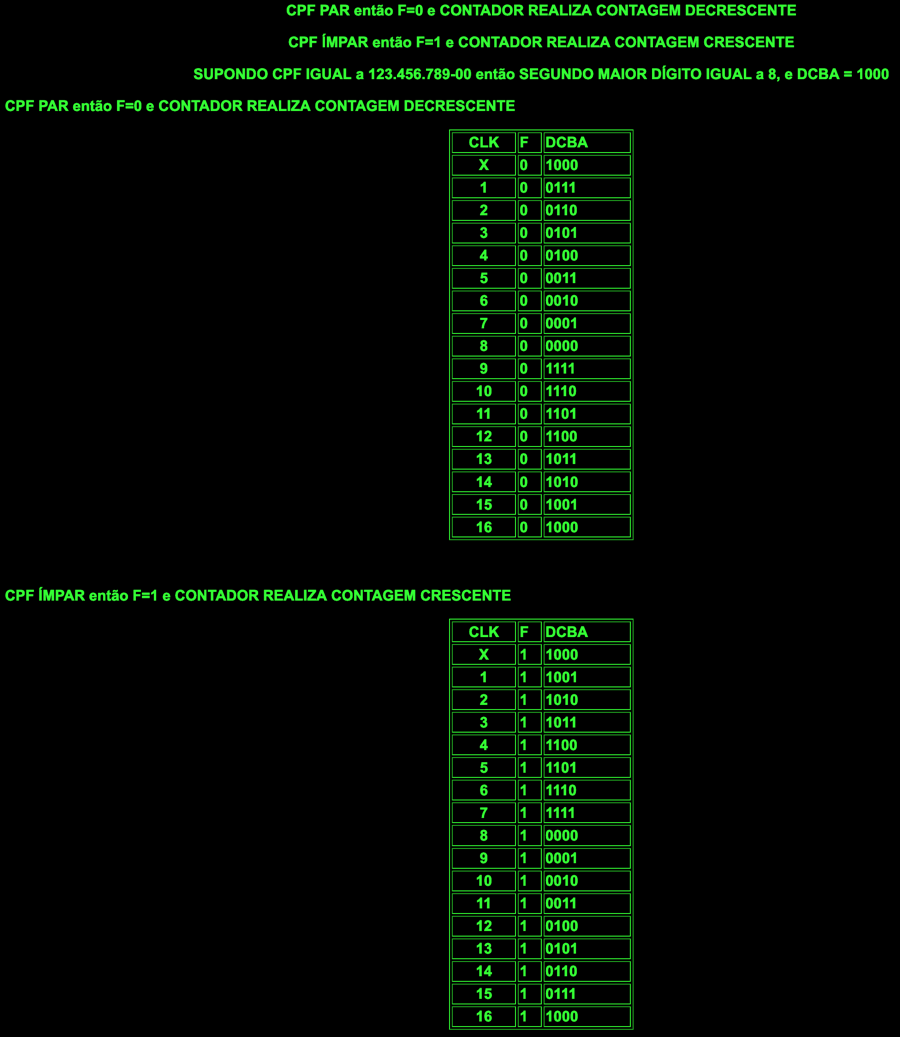

2.A Fig.2 abaixo mostra o circuito lógico do registrador de 4-bits, com clock CLK, entradas D0D1D2D3, e entrada S/L', com as ligações mostradas. No início, o registrador está RESETADO e com as entradas D0D1D2D3 igual à representação em BCD do segundo maior número do seu CPF, então preencha a tabela com os estados do registrador depois de cada transição de gatilhamento do CLK.

Solução

Fig.2

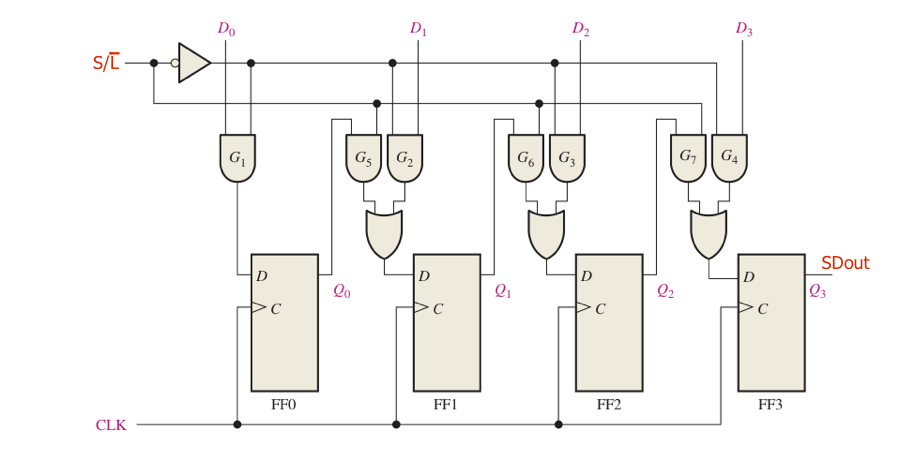

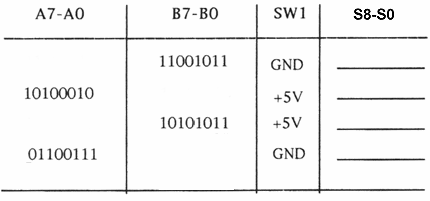

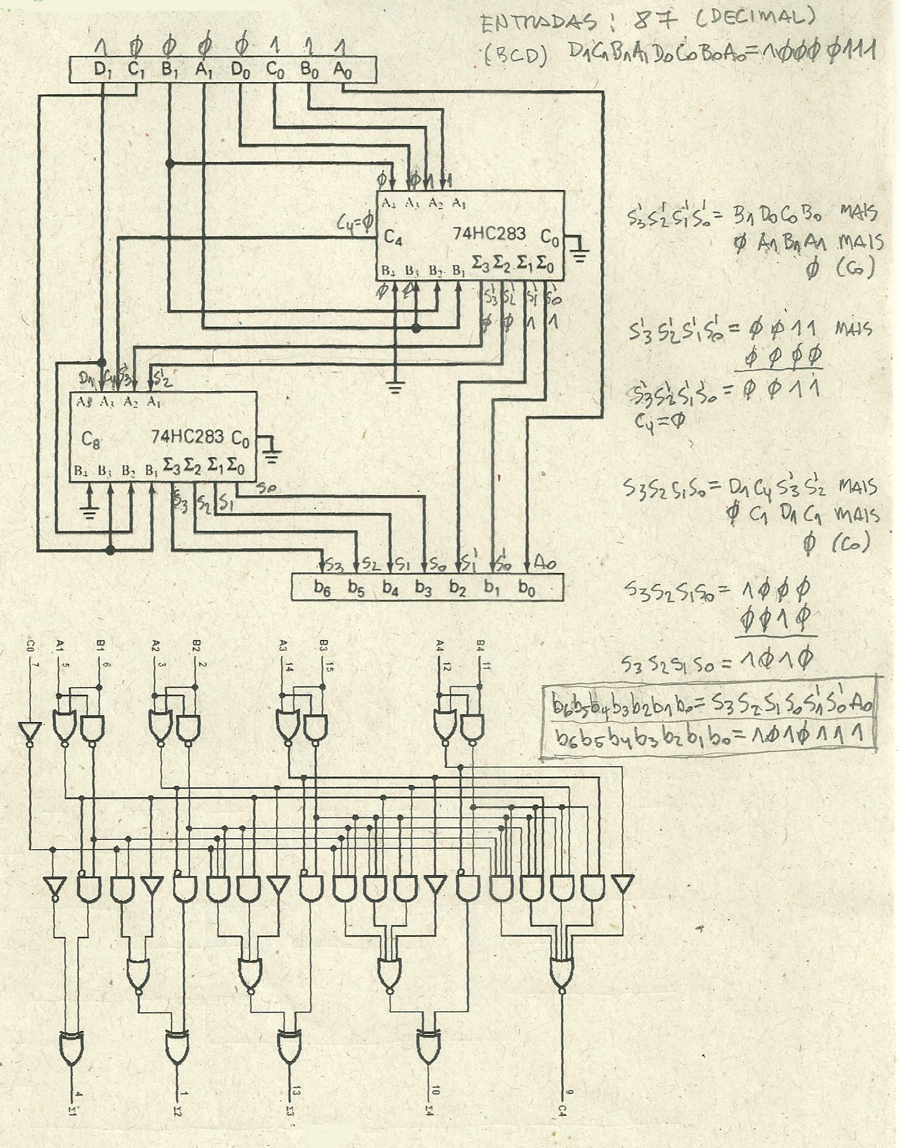

3.Um circuito digital é utilizado para realizar operações com dois números de 8-bits conforme mostra a Fig.3. Determine as saídas S8S7S6S5S4S3S2S1S0 do circuito para cada uma das condições mostradas na tabela e considerando as entradas, não indicadas, A7-A0 iguais à representação BCD dos dois dígitos mais significativos do seu CPF, e B7-B0 iguais à representação BCD dos dois dígitos menos significativos do seu CPF.

Solução

Fig.3

Fig.4

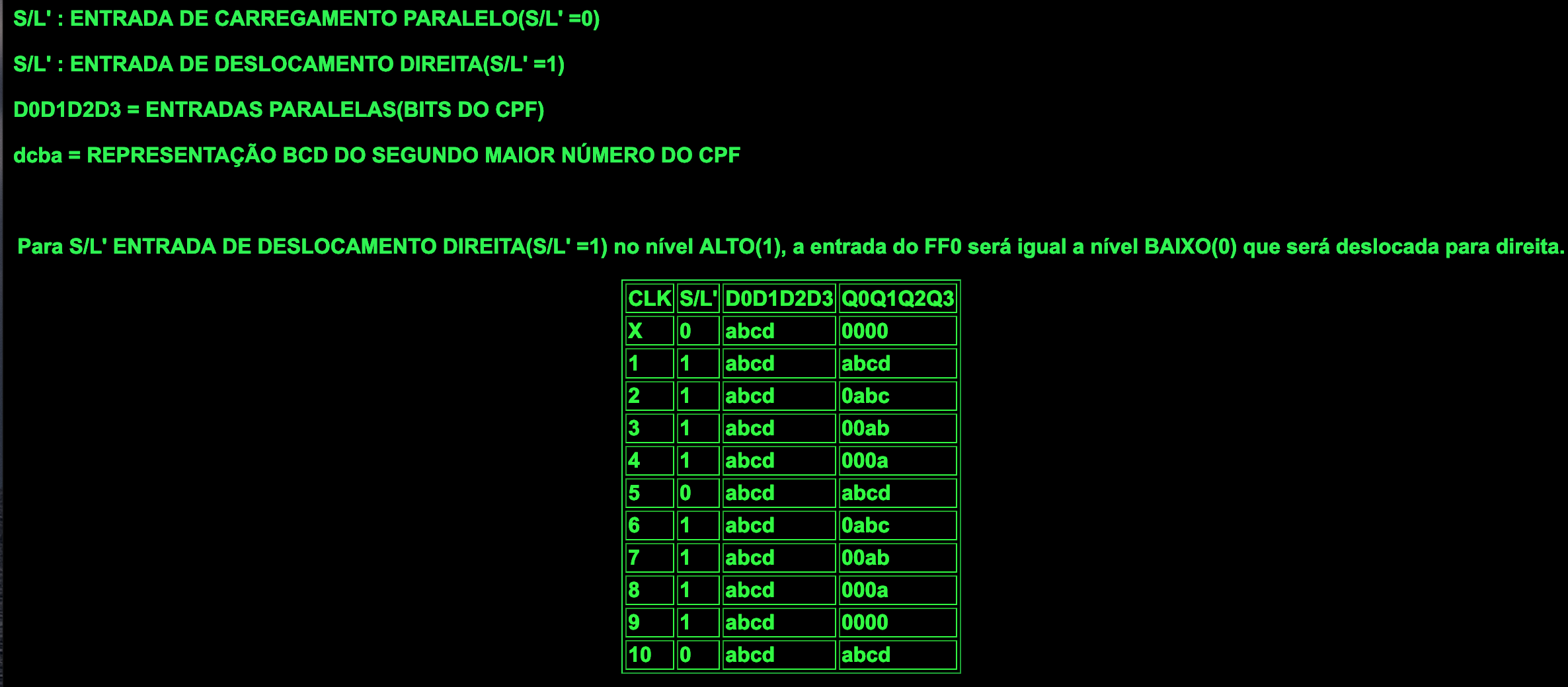

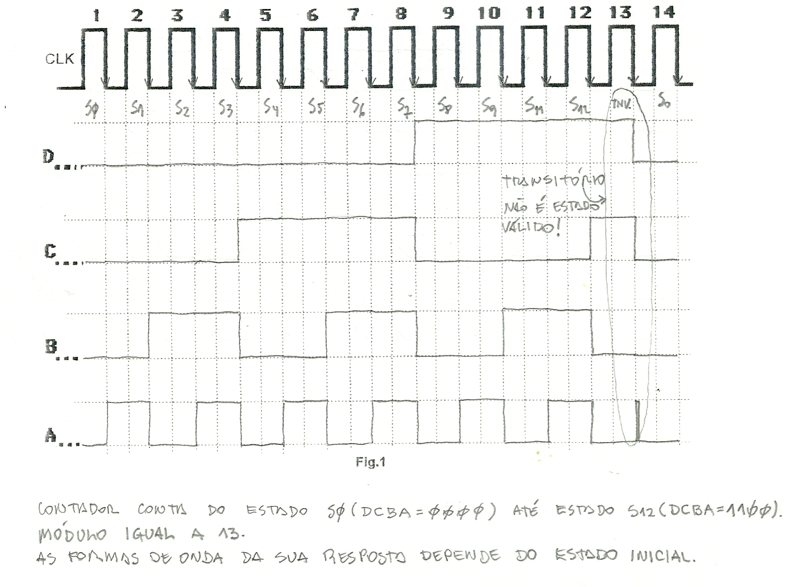

5.A figura abaixo mostra o diagrama lógico de um contador de quatro bits. Analise sua operação e desenhe as formas de onda para cada sinal de saída A, B, C e D e determine o módulo do contador. Use o sinal de clock abaixo e admita que o conteúdo inicial do contador seja igual à representação BCD do segundo maior dígito do seu CPF, se o CPF fôr par; e igual à representção BCD do segundo menor dígito do CPF, se o CPF fôr ímpar.

Solução

Fig.5

Atualizada em 7/05/21