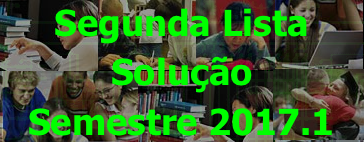

1.Analise o contador assíncrono da Fig.1. Desenhe o diagrama de tempo (formas de onda) e determine a frequência da forma de onda do sinal da saida D do contador. Considere que inicialmente o contador está com DCBA igual à representação BCD do segundo maior dígito do seu CPF e todas as entrada J e K no nível ALTO.

Solução

Fig.1

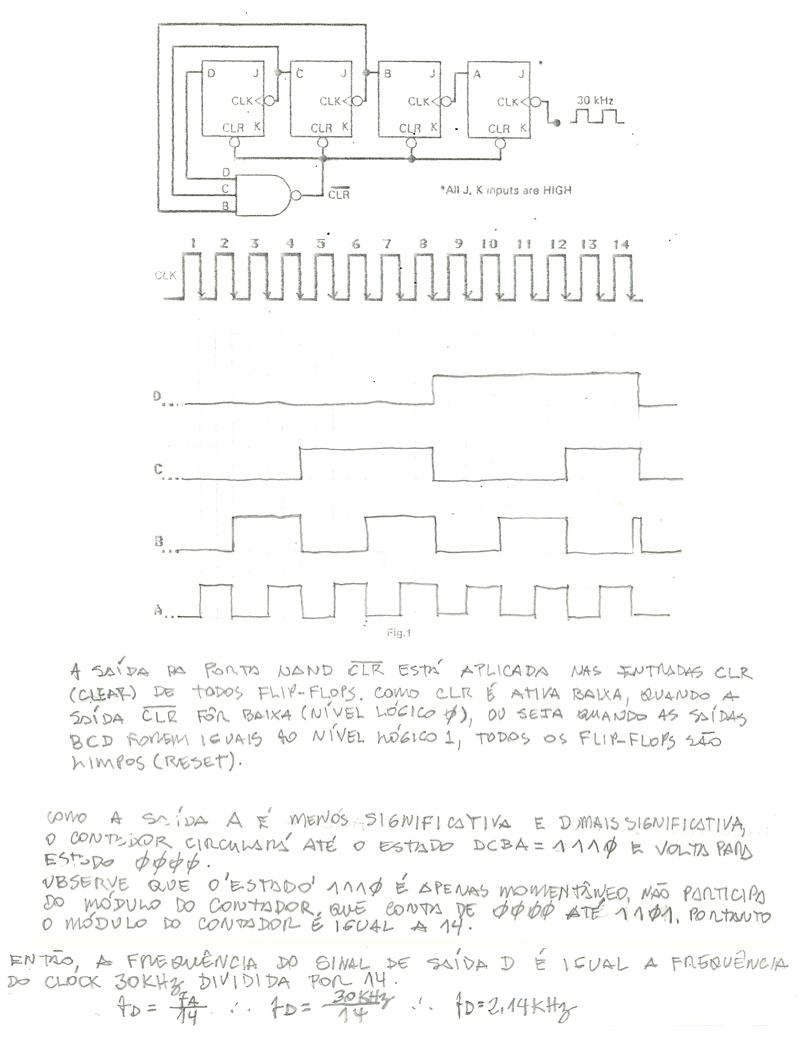

2.Para o somador mostrado na Fig.2, sabendo que A7A6A5A4A3A2A1A0 e B7B6B5B4B3B2B1B0 são iguais a 7210 e 13710, em binário sem sinal, determine as saídas ∑7∑6∑5∑4∑3∑2∑1∑0, C4 e C8. Considere que C0 igual a 1 se seu CPF é ímpar e C0 igual a 0 se seu CPF é par.

Solução

3.O sinal de sincronismo de um circuito digital tem uma freqüência de 35,70MHz e deseja-se um sinal de saída com freqüência igual a 2,55MHz. Empregando somente o CI 7493 abaixo e uma porta AND de duas entradas, projete o circuito indicando claramente a entrada, a saída e todas as conexões necessárias.

Solução

|

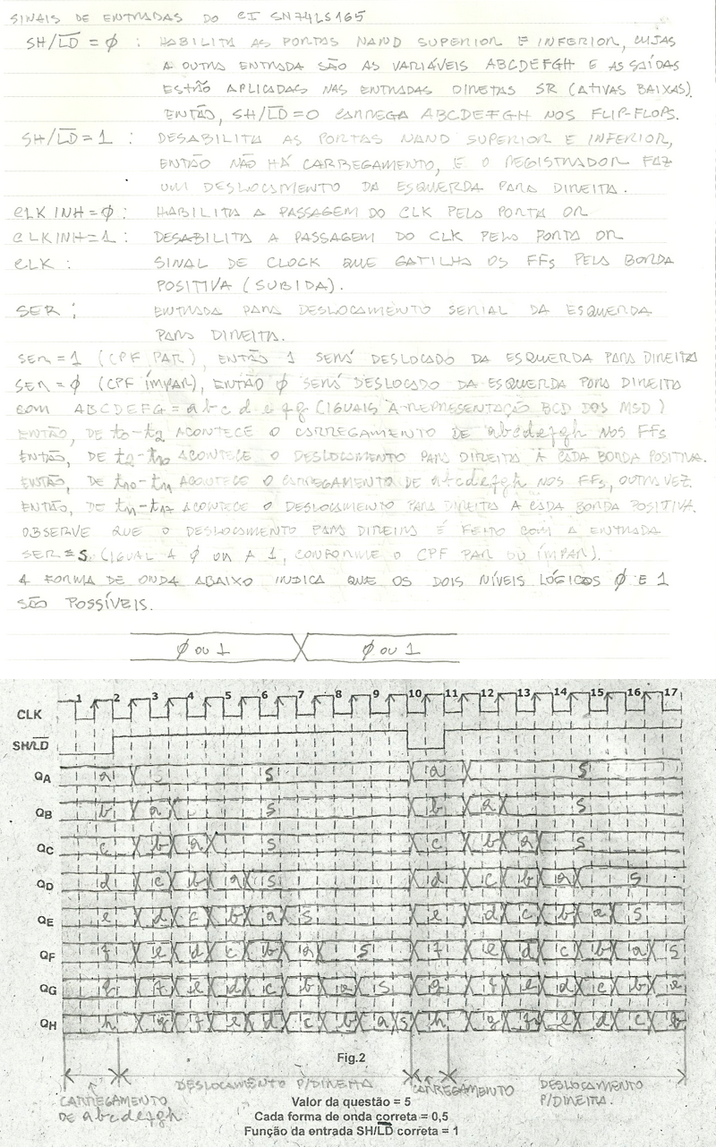

4. A figura abaixo mostra o circuito lógico do registrador SN74LS165, com flip-flps tipo D, providos de entrada diretas set(S) e reset(R), entrada de dados 1D e clock C1. Inicialmente todos os flip-flops no estado RESET, e do instante t=1 até t=17, ABCDEFGH são iguais a representação BCD dos dígitos mais significativos do seu CPF, então desenhe as formas-de-onda das saídas QA, QB, QC, QD, QE, QF, QG e QH para os sinais de entrada mostrados e explique a função da entrada SH/LD. Considere CLK INH = 0 com SER = 1 para CPF par e SER = 0 para CPF ímpar.

Solução

Fig.4

5.A figura abaixo mostra o diagrama lógico de contador de quatro bits. Analise sua operação, determine o módulo e desenhe as formas de onda para cada sinal de saída A, B, C e D. Use o sinal de clock abaixo e admita que o conteúdo inicial do contador seja igual à representação BCD do segundo maior dígito do seu CPF, se o CPF fôr par; e igual à representção BCD do segundo menor dígito do CPF, se o CPF fôr ímpar.

Solução

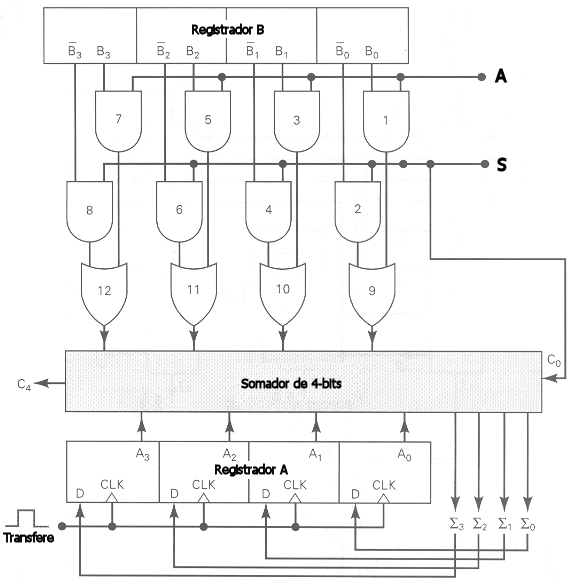

6. O circuito da Fig.6 é utilizado para realizar operações aritméticas de dois números de 4-bits disponíveis nos Registradores A e B. O tipo de operação executada depende do nível lógico nos terminais de controle A e S, e o resultado da operação é registrado após o pulso Transfere. Considere que no Registrador A está armazenado o dígito mais significativo e no Registrador B o dígito menos significativo do número do seu CPF, determine:

(a) Se A=1 e S=0, o conteúdo do Registador A depois do pulso Transfere.

(b) Se A=0 e S=1, o conteúdo do Registrador A depois do pulso Transfere.

(c) O intervalo [-a, +b] de operação do circuito.

(d)

O sistema de representação de números binários com sinal utilizado.

(e) Para C4 = 1, o resultado da operação é válido?

Solução

Fig.6

7.Determine as representações por complemento-de-dois no sistema binário dos seguintes números decimais. Use o menor registrador possível.

Solução

Fig.7

8.O circuito somador 74283, cujo diagrama lógico está na figura abaixo, é um somador de dois números de quatro bits cada. Sabendo que A7A6A5A4A3A2A1 é igual `a representação BCD dos dois dígitos mais significativos e B7B6B5B4B3B2B1 é igual `a representação BCD dos dois dígitos menos significativos do seu CPF, então, na configuração abaixo, determine:

(a)Em que sistema de representação opera o circuito?_____________________________________________________

(b)Qual o intervalo de operação do circuito(maior número positivo e menor número negativo)?___________________

(c)Qual a função da chave SW1 quando está fechada? E quando está aberta?__________________________________

(d)Se SW1 está fechada, determine S8S7S6S5S4S3S2S1.________________________

(e)Se SW1 está aberta, determine S8S7S6S5S4S3S2S1.__________________________

Solução

|

|

9.A tabela abaixo apresenta os quatro valores de dois números

de 8-bits na representação complemento-de-dois. Para cada

linha, determine o resultado da operação indicada na representação

complemento-de-dois.

Solução

10.A figura abaixo mostra dois circuitos seqüênciais e as formas-de-ondas dos sinais de entrada. Supondo que os circuitos estão inicialmente no estado reset, explique a diferença entre os sinais CLK e EN e desenhe as formas-de-ondas dos sinais de saída X e L.

Solução

|

Atualizada em 27/06/17