Roteiro

- As questões deste guia de estudos foram escolhidas de provas anteriores e do livro texto, para preparar você para a segunda prova do curso no Semestre 2025.2

- Leia o assunto relativo a cada questão no livro texto(aconselhável), na homepage ou em notas de aulas, antes de tentar a solução.

- As soluções são descobertas enquanto tenta resolver as questões. Se cometer alguns erros , considere isto parte do processo de aprendizagem.

- Tente resolver sem qualquer ajuda externa(livro, anotações ou colegas).

- Um melhor rendimento é obtido se você resolver cada questão, assim pode medir seu nível de aprendizado.

- Para cada problema determine uma solução completa, incluindo tabelas, equações e circuitos.

- Simplifique as equações dos problemas que exigem simplificação.

- Após resolver os exercícios, verifique sua solução, comparando com outras soluções de colegas e, por último, com as respostas, clicando nos links Solução, abaixo do enunciado de cada questão

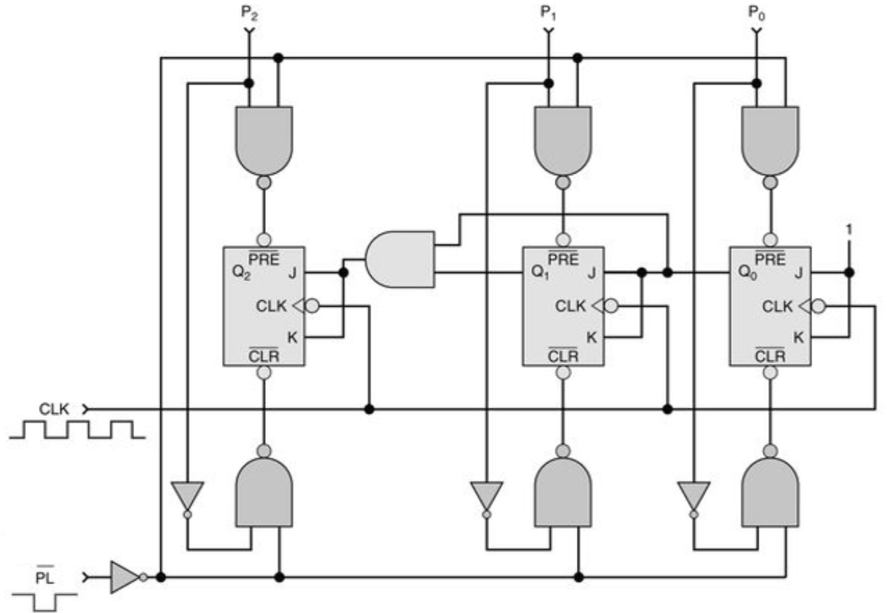

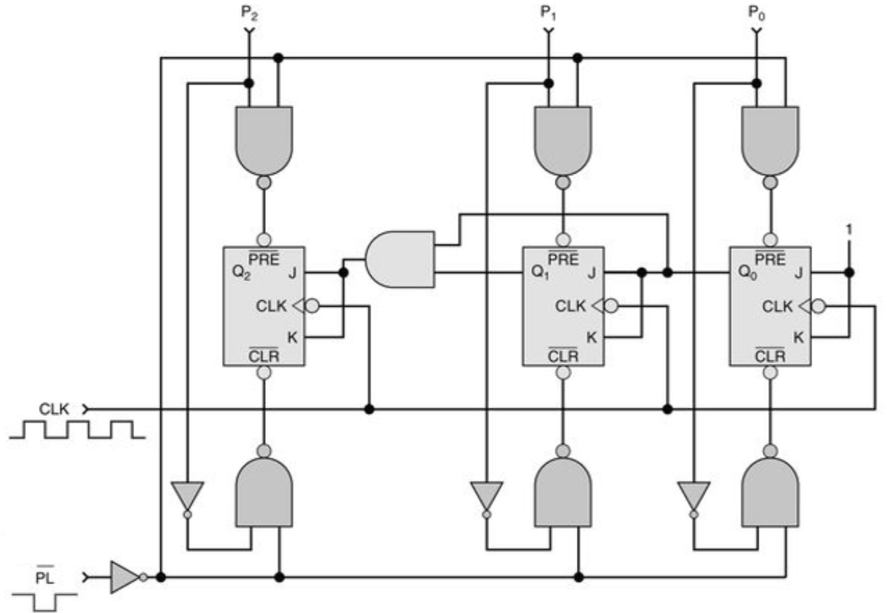

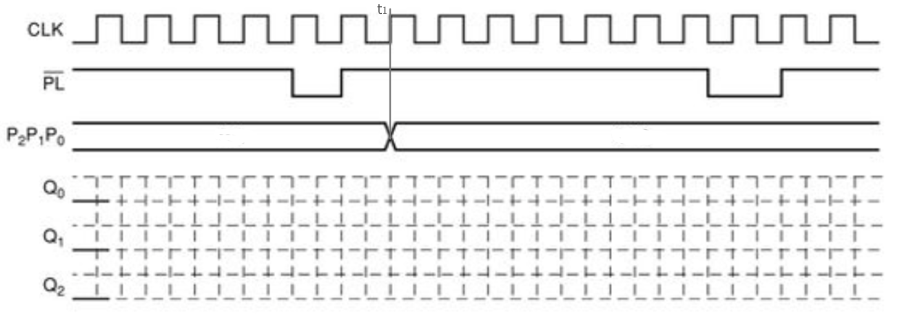

1. Complete o diagrama de tempo da Fig.1 para o contador carregável mostrado. A condição inicial P2P1P0 do contador é igual a 101 até t1 e 010 depois de t1 para CPF par; e igual a 010 até t1 e 101 depois de t1 para CPF ímpar.

Solução

Fig.1

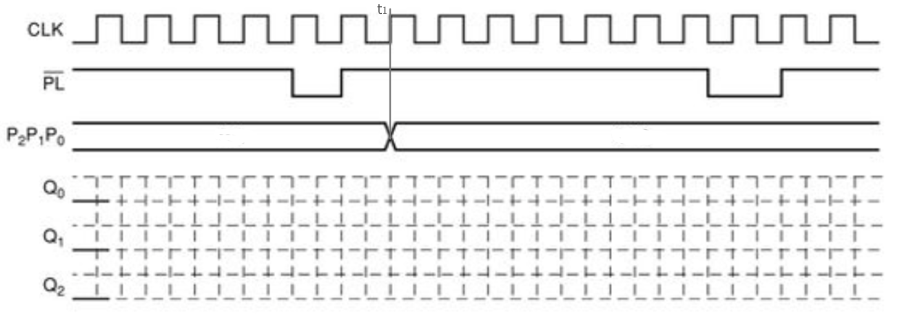

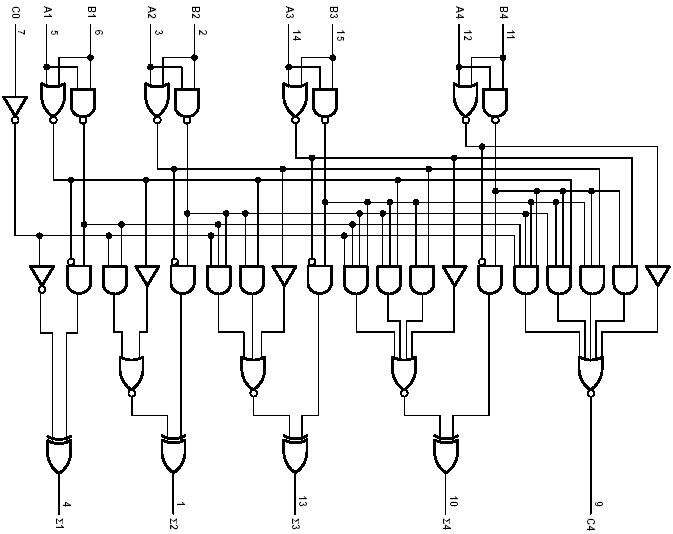

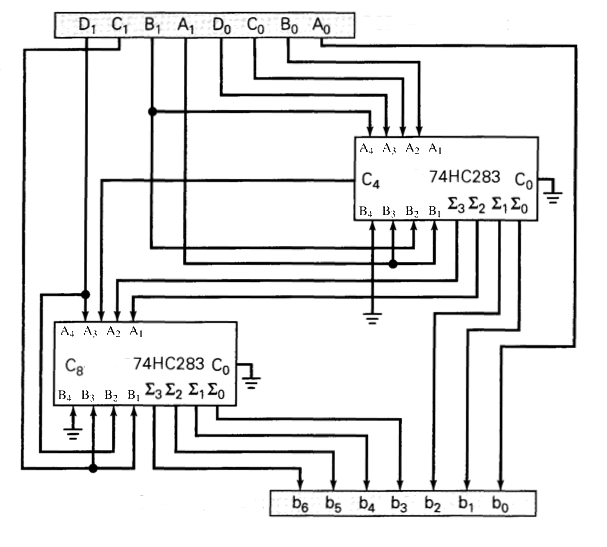

2.Para o circuito com o CI 74HC283 mostrado na Fig.2, sabendo que

D1C1B1A1 e D0C0B0A0 são iguais `as representações BCD dos dois números mais significativos do seu CPF, determine as saídas

b6b5b4b3b2b1b0.

Solução

Fig.2

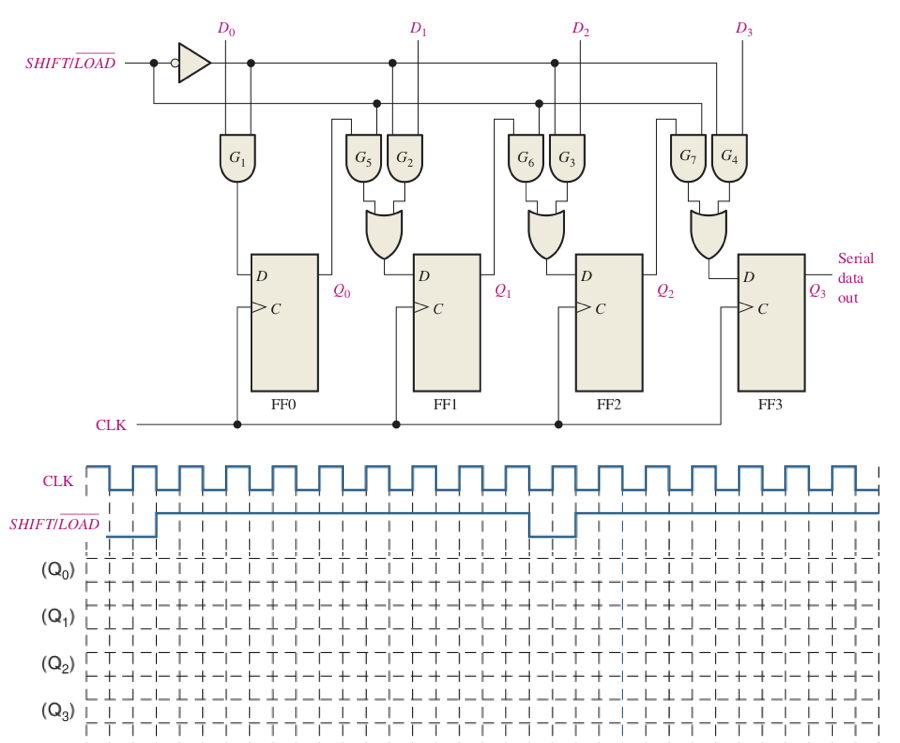

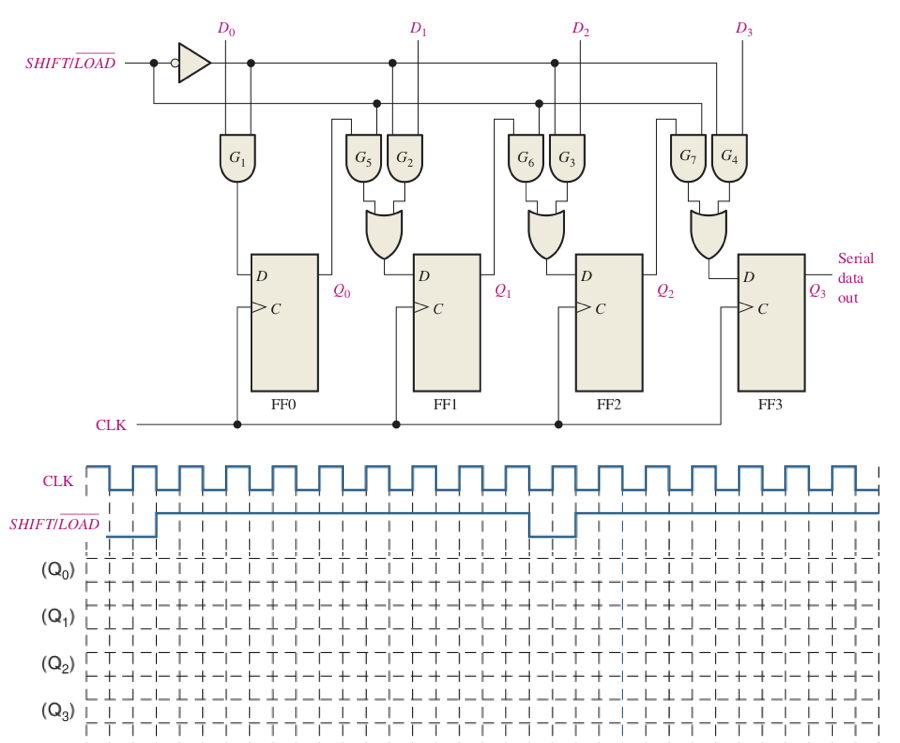

3.A Fig.3 abaixo mostra o circuito lógico do registrador de 4-bits, com clock CLK, entradas D0D1D2D3, e entrada SHIFT/LOAD`, com as ligações mostradas. No início, o registrador está RESETADO e com as entradas D0D1D2D3 iguais à representação em BCD do segundo maior número do seu CPF, então responda as questões abaixo.

a) Função da entrada SHIFT/LOAD`= 0 (CPF par) e SHIFT/LOAD`= 1 (CPF ímpar)

b) Desenhe as formas de ondas das saídas Q3Q2Q1Q0 do registrador.

Solução

Fig.3

CPF = ________________________

Segundo maior número = ________

Entradas D3D2D1D0 = ____________(BCD)

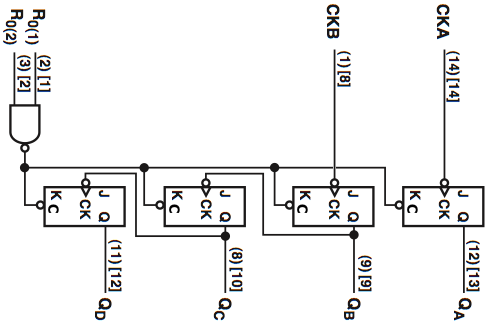

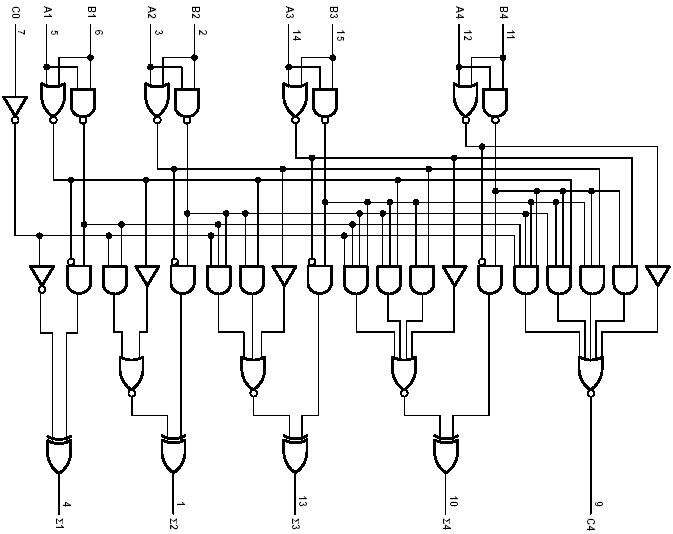

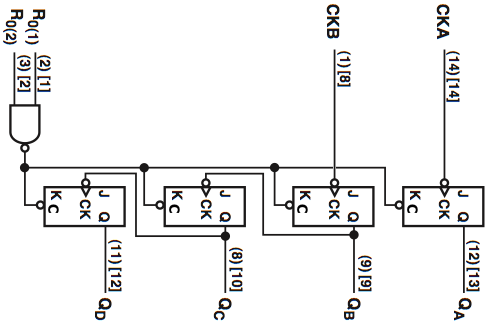

4. O sinal de sincronismo de um circuito digital tem uma freqüência de entrada CKA igual a 36,60MHz e deseja-se um sinal de saída fout com freqüência igual a 2,81MHz. Empregando somente o CI 74LS93 abaixo e uma porta AND de duas entradas, projete o circuito indicando claramente a entrada, a saída e todas as conexões necessárias. As entradas dos flip-flops são J=K=1 e C é o terminal de RESET(CLEAR).

Solução

Fig.4

Atualizada em

5/12/25