1.Um circuito digital tem nas entradas dois números binários de dois bits X=X2X1 e Y=Y2Y1. A saída do circuito é um número binário S=S2S1S0 que é igual ao resultado da soma(adição) de X mais Y, se seu CPF é par e igual ao resultado da magnitude da diferença(subtração) de X menos Y, se seu CPF é ímpar. Projete o circuito somador utilizando a menor quantidade possível de portas NAND mostradas. Indique claramente todas as entradas e saídas das portas lógicas.

Solução

Fig.1

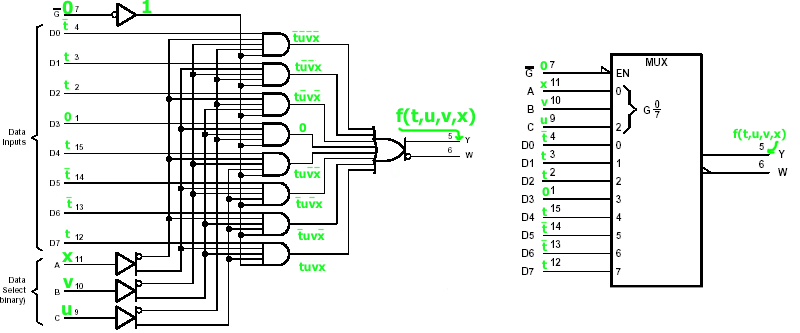

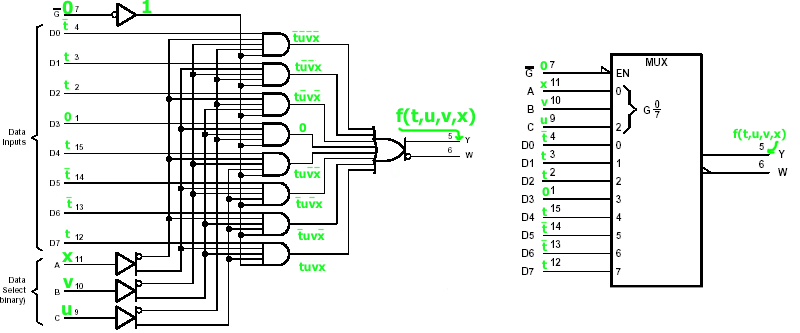

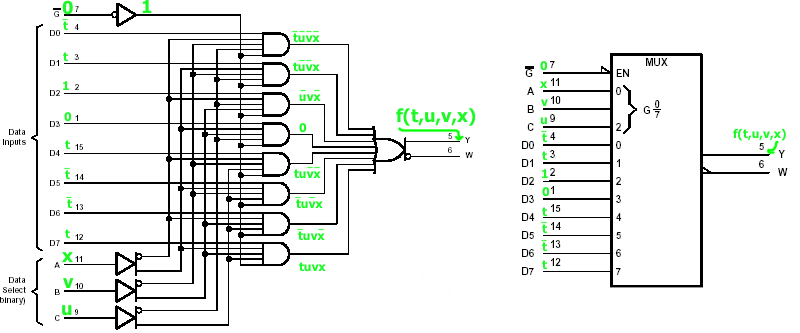

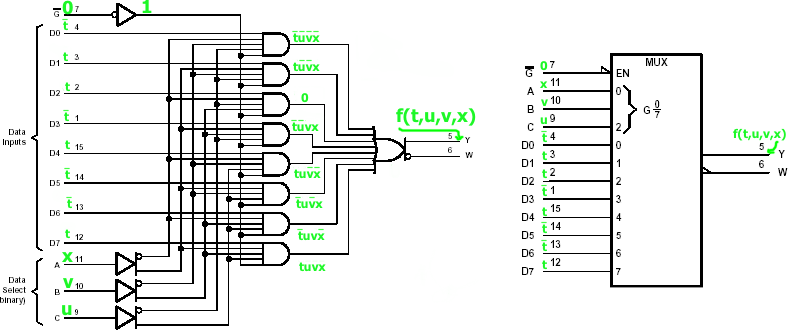

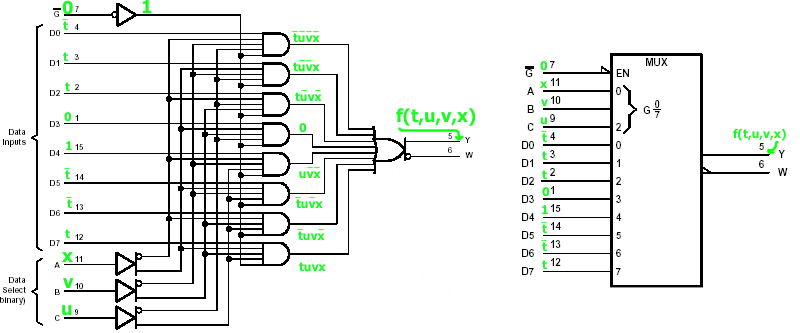

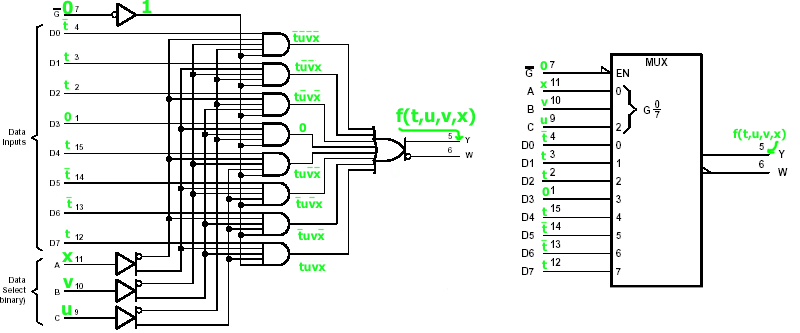

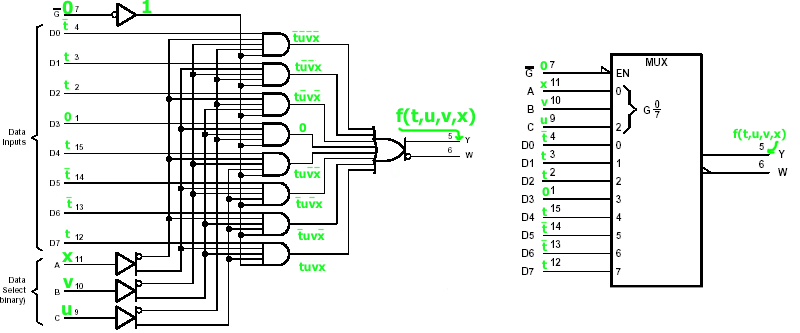

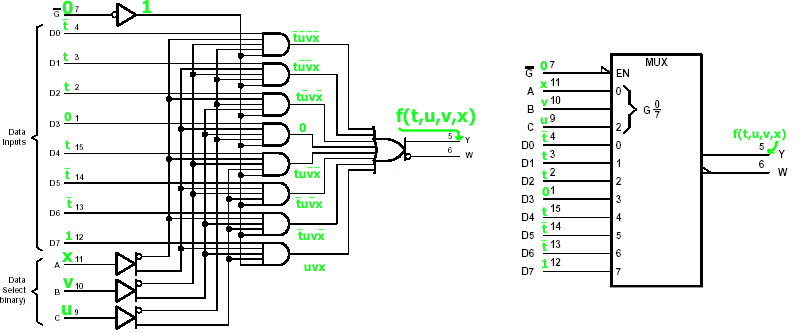

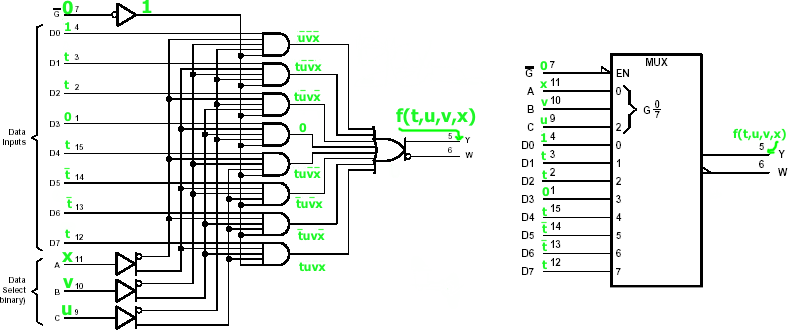

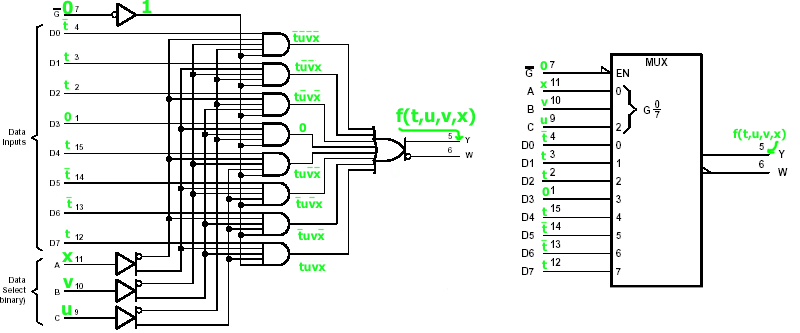

2.Utilizando somente o CI multiplexador 74AS151 mostrado na Fig.2 abaixo, complemente a Fig.2B de modo que a saída Y seja igual à função lógica das variáveis de entrada t, u, v, x e Y= f(t,u,v,x) é dada por

Y = f(t,u,v,x) = Σm(0,mi,5,6,9,10,12,15)

Considere mi igual ao quarto menor dígito do seu CPF. Mostre todas as entradas e a saída na Fig.2B.

Solução

f(t,u,v,x) = ________________________________________

|

|

|

Fig.2A |

Fig.2B |

Dígito do CPF |

mi |

Σm(0,mi,5,6,9,10,12,15) |

f(t,u,v,x) |

0 |

0 |

(0,5,6,9,10,12,15) |

|

1 |

1 |

(0,1,5,6,9,10,12,15) |

|

2 |

2 |

(0,2,5,6,9,10,12,15) |

|

3 |

3 |

(0,3,5,6,9,10,12,15) |

|

4 |

4 |

(0,4,5,6,9,10,12,15) |

|

5 |

5 |

(0,5,6,9,10,12,15) |

|

6 |

6 |

(0,5,6,9,10,12,15) |

|

7 |

7 |

(0,5,6,7,9,10,12,15) |

|

8 |

8 |

(0,5,6,8,9,10,12,15) |

|

9 |

9 |

(0,5,6,9,10,12,15) |

mi = 0

|

Fig.2

|

mi = 1

|

Fig.2 |

mi = 2

|

Fig.2 |

mi = 3

|

Fig.2 |

mi = 4

|

Fig.2 |

mi = 5

|

Fig.2 |

mi = 6

|

Fig.2 |

mi = 7

|

Fig.2 |

mi = 8

|

Fig.2 |

mi = 9

|

Fig.2 |

3.O circuito de alarme mostrado na Fig.3 é utilizado para alarmar determinada situações indesejadas da porta, faróis e ignição de um automóvel. As tres chaves são usadas para sinalizar o estado da porta do motorista, da ignição e dos faróis. Projete o circuito lógico com essas tres chaves como entradas, de modo que o alarme seja ativado( LED aceso ) sempre que ocorrer uma das seguintes situações:

a) Os faróis estão acesos e a ignição está desligada;

b) A porta está aberta e a ignição está ligada.

Se seu CPF é par, use somente portas NAND no projeto do circuito lógico e, caso seu CPF seja ímpar, use somente portas NOR. Empregue a menor quantidade possível de portas lógicas.

Solução

|

|

Fig.3 |

Circuito Lógico |

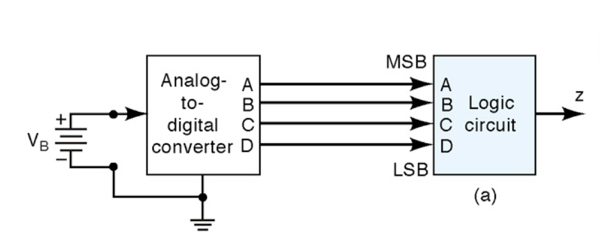

4.O circuito da Fig.4 mostra um conversor analógico-digital monitorando a tensão CC(VB) de uma bateria de 12V. A saída do conversor fornece um número binário de quatro bits ABCD, que corresponde `a tensão da bateria em degraus de 1V, onde A é o dígito mais significativo. As saídas binárias ABCD do conversor são entradas de um circuito lógico que gera uma saída Z que será ALTA para indicar quando a tensão da bateria for maior ou menor que 6V. Desenhe o circuito lógico detetor da tensão da bateria, considerando as seguintes condições:

(a)Seu CPF é par, então o detetor da tensão da bateria deve indicar a saída Z ALTA quando a tensão VB fôr MENOR que 6V;

(b)Seu CPF é ímpar, então o detetor da tensão da bateria deve indicar a saída Z ALTA quando a tensão VB fôr MAIOR que 6V;

Use a menor quantidade possível de portas lógicas.

Solução

|

|

Fig.4 |

Circuito Lógico |

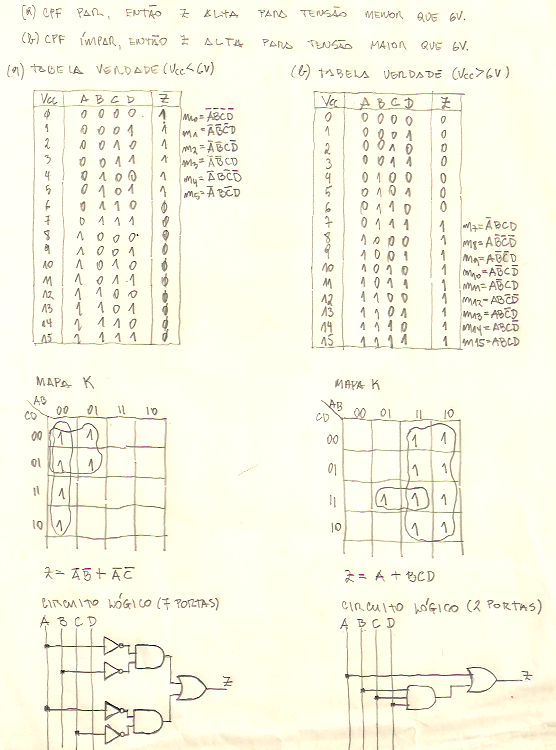

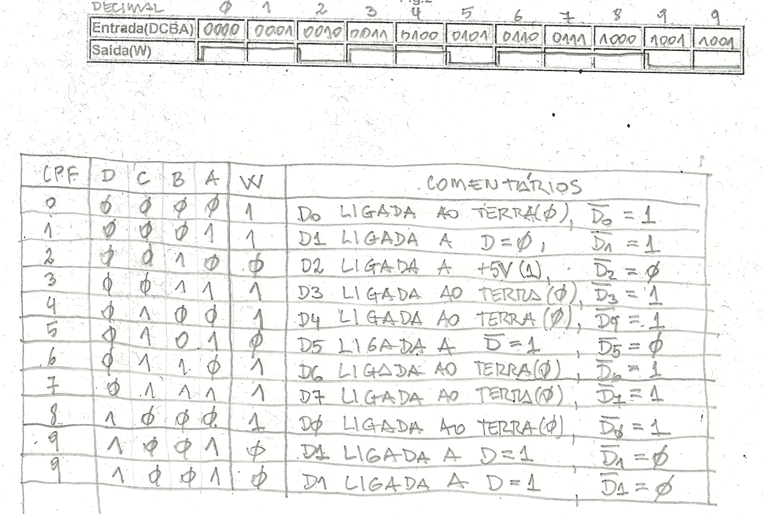

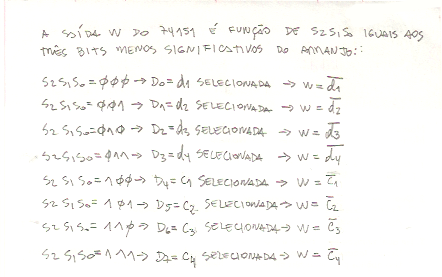

5.No circuito da Fig.5, o CI 74HC151 tem como entradas os sinais DCBA e a saída W. Considerando que as entradas DCBA representam o código BCD dos dígitos de seu CPF, aplicados do dígito mais significativo até o menos siginificativo, desenhe a forma-de-onda do sinal de saída W para toda a sequência das entradas.

Solução

|

|

6.Um código BCD estea sendo transmitido para um receptor remoto. Os bits são DCBA, D sendo o bit mais significativo. O receptor remoto inclui um circuito digital detetor de erro BCD que verifica o código e deteta se o código está correto. Desenhe o circuito detetor de erro BCD utilizando as portas NAND de duas entradas abaixo.

Use Mapas K para simplificar as equações.

Solução

Fig.6

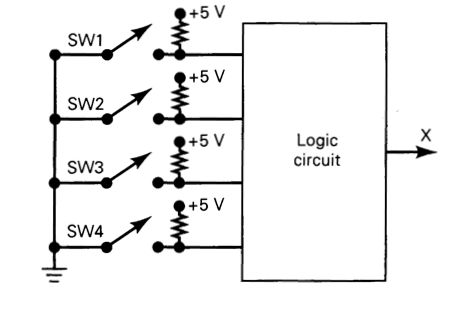

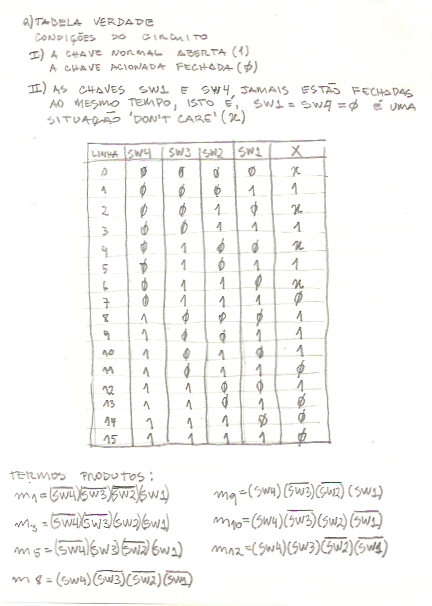

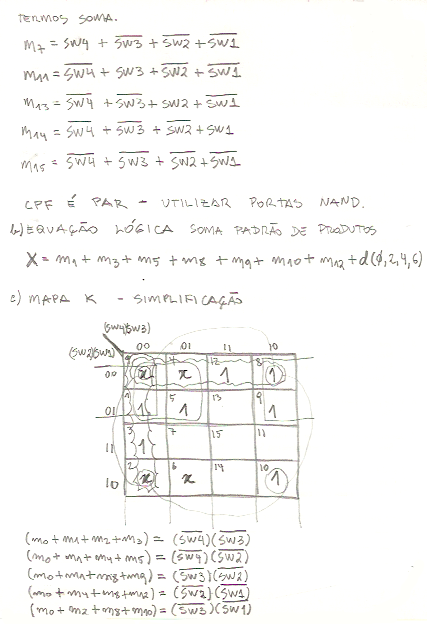

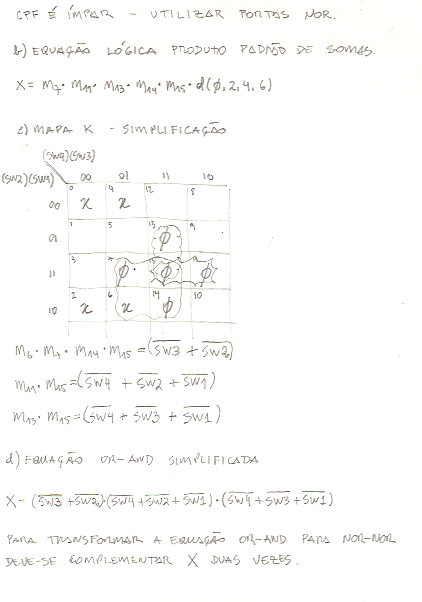

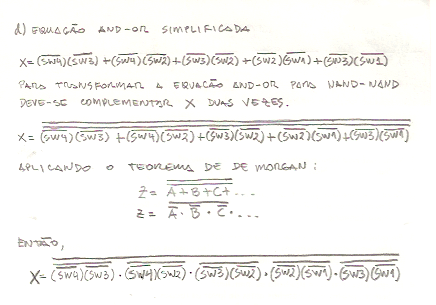

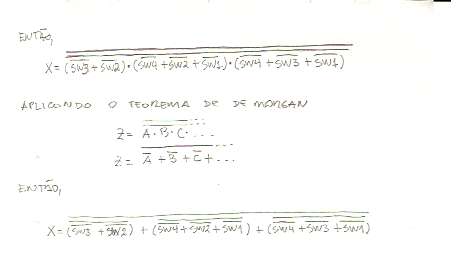

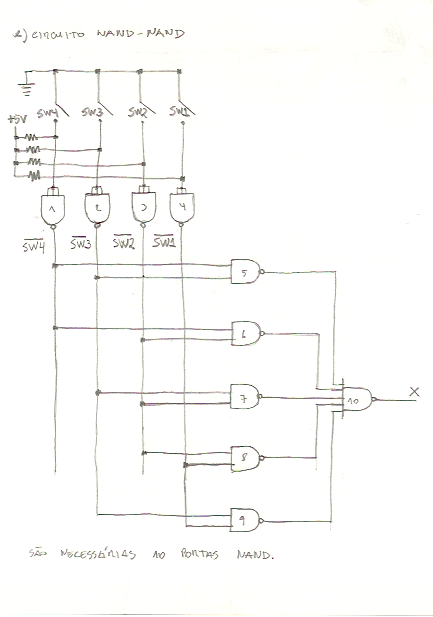

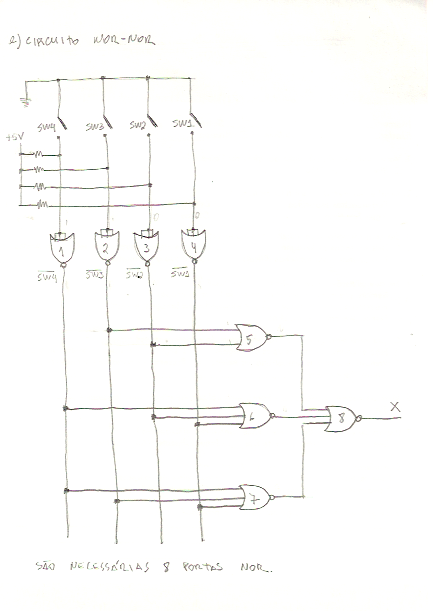

7.A Fig.7 mostra um diagrama para um circuito com quatro chaves de entrada SW1, SW2, SW3 e SW4 que fazem parte do controle de uma máquina copiadora. As chaves são posicionadas em diversos pontos ao longo da trajetória do papel dentro da máquina. Cada chave está no estado normal aberta e, quando o papel passa sobre a chave ela é fechada. É impossível o fechamento simultâneo das chaves SW1 e SW4.

Projete o circuito lógico que gere uma saída X em nível ALTO sempre que duas ou mais chaves estiverem fechadas ao mesmo tempo. Se o seu CPF fôr par, use a menor quantidade de portas NAND e se o seu CPF fôr ímpar, use a menor quantidade de portas NOR.

Solução

|

|

|

|

|

|

|

|

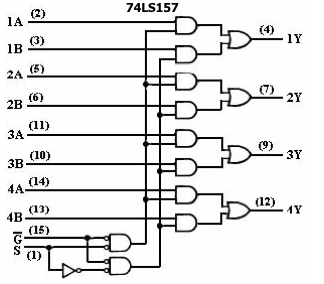

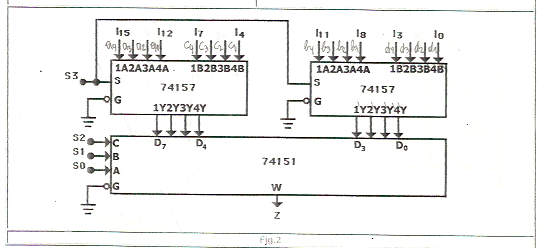

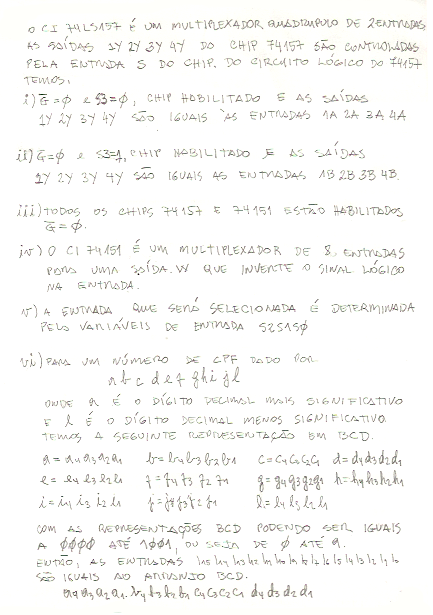

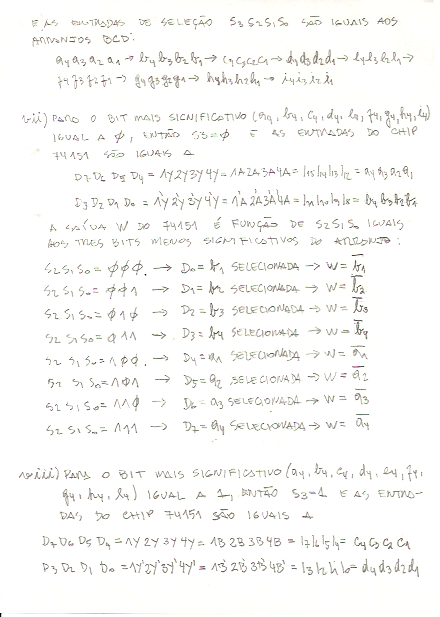

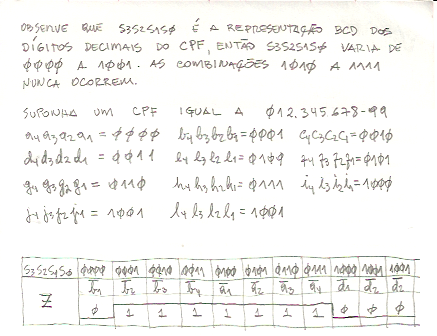

8. Na Fig.8, considere que as entradas I15 até I0 são iguais às representações BCD dos quatro dígitos mais significativos do seu CPF e as entradas S3S2S1S0 são iguais a sequencia das representações BCD dos dígitos do seu CPF, do mais significativo para o menos significativo, um de cada vez. Então, determine a forma de onda da saída Z .

Solução

|

|

|

|

|

|

|

|

Atualizada em 2/10/16