Os contadores síncronos estudados até agora apresentam módulos diferentes, porém sempre são múltiplos de n(número de flip-flops) e não permitem módulos arbitrários com economia de flip-flops.No projeto de um contador de módulo arbitrário, o número de flip-flops deve sempre prover um número de estados igual ou maior que o módulo desejado.

Como o número de estados desejados será sempre menor que o total de estados disponíveis pelos flip-flops, então deve-se decidir quais os estados serão eliminados(estados inválidos) e em que ordem o contador deve passar pelos estados não eliminados(estados válidos), que farão parte da contagem.

| Para prover cinco estados são precisos, no mínimo, três flip-flops(C,B e A) que fornecem oito estados(S0 até S7) mostrados na Fig.1. O próximo passo será escolher o tipo de flip-flop e a seqüência de estados pelos quais o contador circulará. A escolha dos flip-flops pode ser baseada em que flip-flops com uma entrada(tipo D e T) de dados terão equações lógicas grandes e complexas, enquanto flip-flops de dois terminais de entrada(tipo JK e SR) de dados apresentarão mais equações porém as equações são menores e simples.A seqüência de estados de contagem é critério de projeto e depende da aplicação do contador. |

||||||||||||

Fig.1-Estados |

||||||||||||

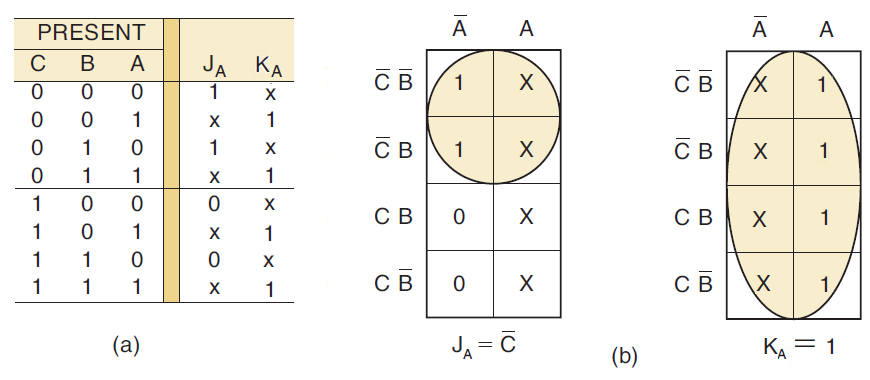

| No caso, os flip-flops serão tipo JK, os estados e a seqüência de contagem é S0, S1, S2, S3, S4. A Fig.2 mostra a Tabela de Estados e Diagrama de Estados para o contador. |

||||||||||||

| Fig.2 - Diagrama e Tabela de Estados | ||||||||||||

|

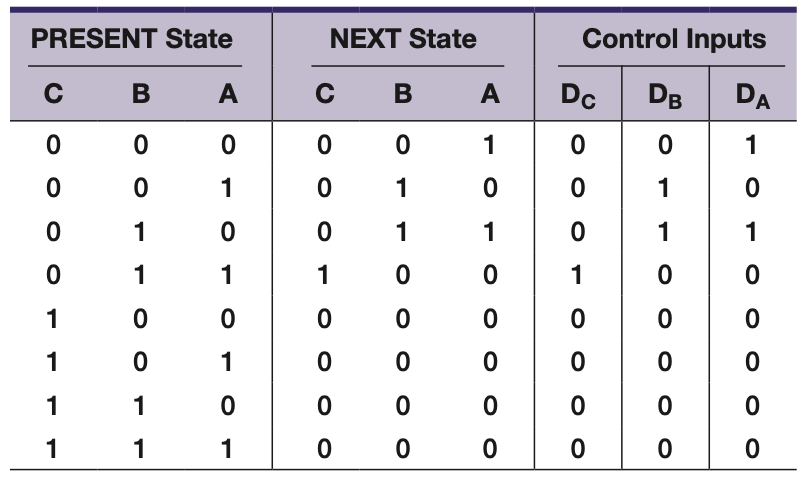

Cada um dos estados acima é caracterizado pelos estados dos flip-flops, isto é, as saídas dos mesmos. Então, substituindo cada estado pela sua atribuição de estados, temos a Tabela de Transição na Fig.3. |

|||||||||||

| Fig.3 - Tabela de Transição | ||||||||||||

| O contador em qualquer dos estados usados precisa dar a cada flip-flop instruções sobre que estado deve assumir quando a próxima transição de gatilho do relógio ocorrer.Então, os terminais de entrada de dados(JAKA, JBKB, JCKC) dos flip-flops são funções das saídas(C, B, e A) dos flip-flops. Para um flip-flop JK se o estado presente é conhecido e o próximo estado é definido, então não é preciso informar os dois níveis lógicos nas entradas JK, conforme mostra a tabela verdade alternativa do flip-flop JK da Fig.4. | ||||||||||||

| Fig.4 - Tabela Verdade FF-JK | ||||||||||||

Fig.5

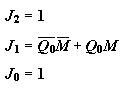

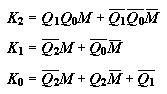

As equações de excitação para os terminais são obtidas da simplificação dos mapas K e estão mostradas abaixo.Como os estados S0, S1, S2 não ocorrem, então colocamos condições irrelevantes nos quadrículos correspodentes a estes estados.

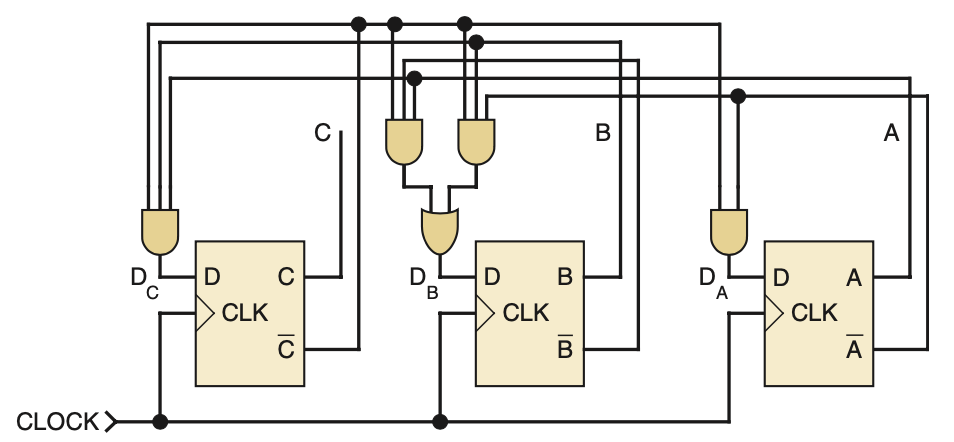

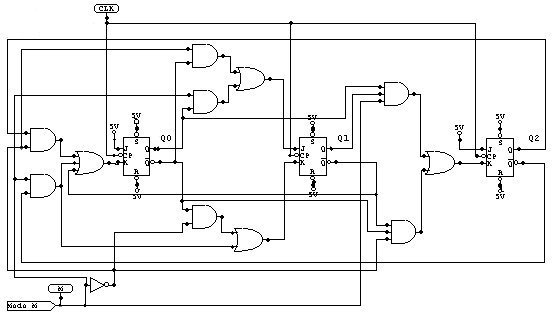

O circuito do contador é composto de três flip-flops JK, algumas portas lógicas, interligados conforme as equações acima. Observe o sinal de sincronismo(relógio) comum a todos os flip-flops do contador.

Fig.6

Contador síncrono módulo 5 - Diagrama de estados

Fig.11

|

|

|

|

|

|

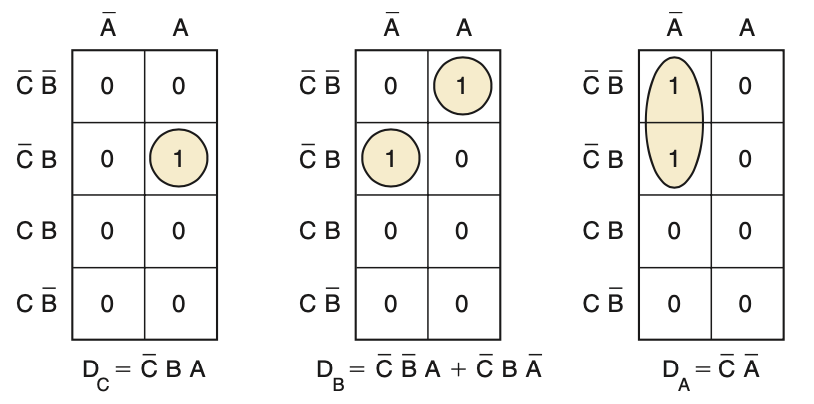

A solução dos mapas K fornece as equações de excitação das entradas dos flip-flops, conforme mostrado abaixo.

|

|

O circuito do contador é composto de três flip-flops interligados com algumas portas lógicas de acordo com o conjunto de equações de excitação acima.Observe as formas-de-onda dos sinais de entrada e saídas do contador.

|

Contador Assíncrono - o sinal de relógio(sincronismo) não é aplicado a todos os flip-flops; a entrada de relógio de alguns flip-flops do contador é a saída de outros flip-flops.

Vantagem: economia de circuitos

Desvantagem: limitação de velocidade

Circuito

Fig.14

Fig.16

Existem vários circuitos integrados contadores em tecnologia CMOS, TTL e outras.Alguns contadores apresentam diversas características e facilidades, outros são bem simples com apenas as características básicas.

| Todos os flip-flops estão no modo chaveamento, entradas J=K=1 |

| MR1 e MR2: entradas de RESET diretas ativas ALTAS |

| FFs B, C, D: contador assíncrono, módulo 8, relógio |

| FF A: contador síncrono, módulo 2, relógio |

| FFs A, B, C, D: contador assíncrono, módulo 16, relógio |

|

CTR: designa que o circuito integrado é um contador; designação pode vir acompanhada da letra m, CTRm, onde m indica o número de bits do contador. DIVm: representa um contador de módulo m, interno ao circuito integrado. No caso, DIV2 representa um contador módulo 2 e DIV8 um contador módulo 8. +: indica uma entrada incrementadora; a cada borda de gatilhamento do relógio(CK), o contador incrementa. CT=0: indica que quando as entrada R0(1) e R0(2) estão ativas, ALTAS, o contador assume a contagem decimal 0, correspondente a saída QAQBQCQD=0000. |

|||||||

| Fig.18 | ||||||||

Fig.19

|

|

||||||||

| Z4: indica uma interconexão interna, isto é, a saída QC(1Z4) está ligada à entrada 4+, sendo 1Z4 ativa ALTA e 4+ ativa na transição BAIXA | |||||||||

| Fig.20 - Símbolo IEEE/ANSI | |||||||||

|

|

Fig.21 - 74LS90 Símbolo lógico |

Fig.22 - Símbolo IEEE/ANSI |

| MR1 e MR2: entradas de RESET diretas ativas ALTAS |

| MS1 e MS2: entradas de SET diretas ativas ALTAS |

| FF A: contador síncrono, módulo 2, relógio |

| FFs B, C, D: contador assíncrono, módulo 5, relógio |

| FFs A, B, C, D: contador assíncrono, módulo 10(década), relógio |

|

Circuitos Integrados Contadores |

|

Questões para Revisão - verifique e consolide os conhecimentos vistos acima sobre contadores e suas aplicações.Clique aqui! | |

Atualizada em 19/07/24