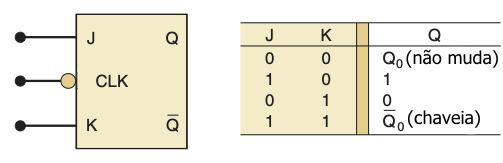

A Fig.1 abaixo mostra uma versão simplificada do circuito de um flip-flop tipo JK, com entrada de relógio(sincronismo ou clock). As entradas J e K controlam o estado do FF, semelhante às entradas S e R do flip-flop tipo SR, porém com uma diferença: a condição J=K=1 não produz um estado ambíguo na saída.

Na verdade, a única diferença entre os dois circuitos é que as saídas Q e Q' são realimentadas para as portas NAND de entrada de dados 1A e 1B. Essa conexão de feedback é o que dá ao flip-flop JK sua operação de alternância para a condição J = K = 1. Para essa condição, o FF-JK sempre irá para o estado oposto em que se encontra. Diz-se que o FF está no modo de comutação ou chaveamento(toggle mode). Neste modo, se ambas as entradas J e K estão ATIVAS, o FF muda de estado(comuta) a cada período do relógio.

Os níveis lógicos nas entradas das portas 1A e 1B determinam se o sinal de relógio ajusta(SET) ou reajusta(RESET) o flip-flop. Agora, o estado seguinte do flip-flop é determinado pelas entradas J, K, relógio e também pelas saídas atuais do flip-flop, isto é, pelo estado atual.

- J=K=0:

- as portas 1A e 1B desabilitadas; o relógio não muda o estado do flip-flop

- J=0, K=1:

- se Q=0, a porta 1A desabilitada, a porta 1B desabilitada; o relógio não muda o estado do flip-flop

- se Q=1, a porta 1A desabilitada, a porta 1B habilitada; o relógio muda o estado do flip-flop para RESET

- J=1, K=0:

- se Q=0, a porta 1A habilitada, a porta 1B desabilitada; o relógio muda o estado do flip-flop para SET

- se Q=1, a porta 1A desabilitada, a porta 1B desabilitada; o relógio não muda o estado do flip-flop

- J=K=1:

- se Q=0, a porta 1A habilitada, a porta 1B desabilitada; o relógio muda o estado do flip-flop para SET

- se Q=1, a porta 1A desabilitada, a porta 1B habilitada; o relógio muda o estado do flip-flop para RESET

Então, para J=K=1, a cada ciclo de relógio o estado do flip-flop JK se altera(chaveia), se está SET vai pra RESET; se está RESET irá para SET. A tabela verdade não tem nenhuma combinação de entrada identificada como "não usada".

A tabela verdade do FF-JK é semelhante à do FF-SR, exceto para a condição J=K=1. Esta condição resulta em uma saída Q igual ao inverso do que era antes do ciclo de relógio(Q=Q0). Esta operação chama-se comutação.

O FF-JK é muito mais versátil que o FF-SR porque não tem estados ambíguos. A condição de entrada J=K=1 produz uma operação de comutação bastante empregada nos contadores binários. O FF-JK pode fazer tudo que o FF-SR faz, além de operar no modo de comutação(chaveamento).

|

Os terminais de entrada de dados, e o flip-flop tipo JK, são assim denominados JK em homenagem ao Prêmio Nobel da Física de 2000, Eng Jack St. Clair Kilby, da Texas Instruments, pela invenção do circuito integrado monolítico - microchip. |

|

| |

|

O flip-flop tipo T(toggle) tem uma única entrada de controle que chaveia o flip-flop quando está ATIVA e quando INATIVA não muda o estado do flip-flop. O flip-flop tipo T é construído conectando juntos os terminais J e K de um FF-JK, como mostra a figura a seguir.

Fig.3

O terminal comum T é o terminal de controle. O flip-flop chaveia quando T=1.

Propriedade de Detecção de 1s

O flip-flop na configuração mestre-escravo tem o latch mestre ligado aos terminais de dados quando o relógio está ALTO e a resposta de saída, se houver, ocorre no relógio no nível BAIXO.

A resposta do flip-flop é determinada por qual entrada esteve no nível lógico ALTO(1), enquanto as portas de entrada estavam habilitadas, como mostra a Fig.4.

As formas-de-onda da Fig.4 mostram que o flip-flop não permanece no estado RESET durante dois ciclos de relógio embora J=K=0, pois no segundo pulso de relógio a entrada J(S) vai para o nível ALTO colocando o flip-flop no estado SET.

Embora J(S) volte para o nível BAIXO, o flip-flop mantem o estado SET.

Esta característica é a propriedade de detecção de 1s do flip-flop mestre-escravo.

Esta característica torna o flip-flop suscetível a perigos e a ruídos.

|

|

|

|

Fig.4

Flip-Flop Gatilhado pela Borda

O problema da detecção de 1s é resolvido com o circuito de um flip-flop gatilhado pela borda.Nesse tipo de flip-flop, a resposta de saída à entrada de dados será determinada pelos dados presentes nos terminais de entrada imediatamente antes da transição de gatilho do sinal de relógio.

A figura abaixo mostra o circuito lógico do flip-flop J-K SN74LS107A, CI com dois flip-flops J-K com CLEAR, gatilhados pela borda e a transição de gatilho é a borda negativa do relógio. O flip-flop usa o atraso de propagação através de uma porta para temporizar o gatilhamento.

No circuito acima, a saída Q da porta 1D é determinada pelas variáveis X e Y. Supondo que há atrasos de propagação nas portas lógicas e que são iguais para todas as portas, então em resposta ao relógio, a variável X muda antes que Y, pois o sinal de relógio se propaga por duas portas para afetar Y e por uma porta para afetar X.

Supondo o flip-flop no estado RESET, Q=0 e, J=1 e K=0, temos:

Relógio BAIXO: X=0, Y=1

Relógio ALTO: X=1, Y=0

Fazendo uma transição positiva do sinal de relógio(do nível BAIXO para ALTO) X muda antes que Y;

X vai para o nível 1; Y vai para o nível 0 as entradas da porta 1D: XY=01-->11-->10 então a saída da porta 1D não muda, pois uma das entradas é sempre 1, e a saída fica em Q=0 e o flip-flop não muda de estado;

Fazendo uma transição negativa do sinal de relógio(do nível ALTO para BAIXO) X muda antes que Y;

X vai para o nível 0; Y vai para o nível 1 as entradas da porta 1D: XY=10-->00-->01 então as entradas XY da porta 1D em um pequeno intervalo de tempo ficam XY=00, levando a saída da porta 1D para Q=1 o flip-flop muda de estado RESET Q=0 para o estado SET Q=1.

O intervalo de tempo no qual X=Y=0 é aproximadamente igual ao tempo do atraso de propagação de uma porta. Se os dados de entrada J e K mudam no último instante antes da transição de gatilhamento, o flip-flop responde à instrução atualizada.

Flip-Flop Tipo D

O flip-flop tipo D tem somente uma entrada de controle síncrona D, que significa dado. A operação do flip-flop D é simples: a saída Q vai para o mesmo nível lógico que está presente na entrada de controle D quando acontece a borda de gatilhamento do sinal de relógio. O nível lógico de D será armazenado no flip-flop quando ocorre o gatilhamento.

O flip-flop D pode ser implementado usando um flip-flop SC(SR) ou JK simplesmente colocando uma porta NOT entre as entradas S e C(R) ou, J e K, como mostra as figuras abaixo.

|

|

Fig.6

|

Fig.7

O flip-flop tipo D atrasa uma seqüência de entradas se a transição de gatilho do relógio for feita imediatamente antes da alteração no valor dos dados de entrada.

Fig.8

Vantagens do flip-flop tipo D:

- Não há problema de corridas devido ao arranjo mestre-escravo

- Não tem problema de deteção de 1s

- Não é afetado pelos tempos de subida/descida do sinal de relógio

Flip-Flop Tipo D Alternativo

Este tipo de flip-flop alternativo é mais econômico que o flip-flop mestre-escravo modificado.

Fig.9

| C=0: |

S'=R'=1

independente de D |

Portas 3A e 3B habilitadas e qualquer estado é possível; o FF mantem o estado anterior |

| |

|

|

| C=0, D=0: |

Fazendo C=1 então

S'=1, R'=0 e Q=0 |

Para C=1 e qualquer alteração em D, S' e R' inalterados.Se C retorna a 0, FF não muda |

| |

|

|

| C=0, D=1: |

Fazendo C=1 então

S'=0, R'=1 e Q=1 |

Para C=1 e qualquer alteração em D, S' e R' inalterados.Se C retorna a 0, FF não muda |

| |

|

|

| Resumindo: |

Transição Positiva:

C:0 ->1 |

Se D=0, então Q=0

Se D=1, então Q=1 |

| |

|

|

|

C=1 |

Alterações em D não mudam Q |

|

Flip-Flop SN74S74

Este CI tem dois flip-flops tipo D gatilhados pela borda positiva .Cada unidade tem entradas de PRESET e CLEAR ativas BAIXAS que leva o FF ao estado SET ou RESET independentemente dos níveis das outras entradas.Quando as entradas diretas estão inativas(ALTAS), o dado na entrada D que obedece ao tempo de manutenção é transferido para saída na borda positiva do pulso do sinal de relógio.Após decorrido o tempo de manutenção, o dado em D pode ser alterado sem afetar os níveis das saídas.

Veja a folha de dados completa para este CI. |

Temporização dos Flip-Flops

Os fabricantes de CIs especificam vários parâmetros e características de temporização que devem ser considerados antes de usar um FF em qualquer aplicação.

Tempos de Preparação(Setup) e de Manutenção(Hold)

O tempo de Preparação(Setup), ts,é o intervalo de tempo precedente à transição do sinal de relógio durante o qual as entradas síncronas devem ser mantidas no nível lógico correto.

Os fabricantes, em geral, especificam o tempo mínimo permitido.

O tempo de Manutenção(Hold), th, é o intervalo de tempo que segue imediatamente a transição ativa do sinal de relógio, durante o qual as entradas síncronas devem ser mantidas no nível lógico correto.

|

|

|

|

Fig.10

Fig.11 Fig.11 |

Sempre que um sinal muda o estado da saída de um FF, existe um atraso entre o instante que o sinal é aplicado para o instante no qual a saída realiza sua mudança.

Estes intervalos são sempre medidos em relação ao ponto médio da transição entre níveis do sinal de relógio.

Os fabricantes especificam os atrasos de propagação em resposta a todas as entradas e tem valores na faixa de nanosegundos, em torno de 100nseg.

|

|

Freqüência Máxima de Chaveamento, fMAX

A Freqüência Máxima de Chaveamento, fMAXé a maior freqüência que pode ser aplicada na entrada de relógio do FF e este ainda pode gatilhar confiávelmente. A fMAX varia de FF para FF mesmo para os flip-flops com mesmo número de fabricação.

Tempos de Pulso de Relógio BAIXO e ALTO

Os fabricantes especificam a duração mínima que o sinal de relógio deve permanecer no nível BAIXO antes de transitar para o nível ALTO, tW(L).

O tempo mínimo que o relógio deve ficar no nível ALTO antes de ir para o nível BAIXO é chamado tW(H).

Fig.12

Os fabricantes também especificam o tempo mínimo de duração que a entrada PRESET ou CLEAR deve permanecer no nível ativo para que o FF seja levado ao estado SET ou RESET confiávelmente.

Para gatilhamento confiável, a forma-de-onda do relógio deve ter tempos de transição(tempos de subida e descida) muito curtos. Se estes tempos são grandes o flip-flop pode gatilhar erradamente ou não gatilhar.Os fabricantes não informam os tempos de transição máximos para os FFs. Em geral, indicam o requesito geral para uma determinada família.

|

Questões para Revisão

Verifique seus conhecimentos e resolva algumas questões para revisão sobre latches e flip-flops.Clique aqui! |

|

Atualizada em

31/10/24

Fig.11

Fig.11