Dispositivos Logicamente Programáveis(PLDs-Programmable Logic Devices)

Existe uma grande variedade de CIs com diversas funções lógicas e arranjos de circuitos lógicos em chips de diversos fabricantes. Porém existem desvantagens em empregar estes CIs em determinados circuitos e sistemas.

Para reduzir o número de CIs a ser usado em certo projeto, é preciso colocar mais funções lógicas dentro do chip.Isto é feito com aplicações das tecnologias LSI e VLSI para funções padrões da microeletrônica. Porém há situações de projeto que não existem CIs LSI e VLSI que atendam os requisitos de projeto. A solução que a indústria apresentou foi um dispositivo que substitui vários CIs MSI e SSI padrões, em um único CI: os PLDs.

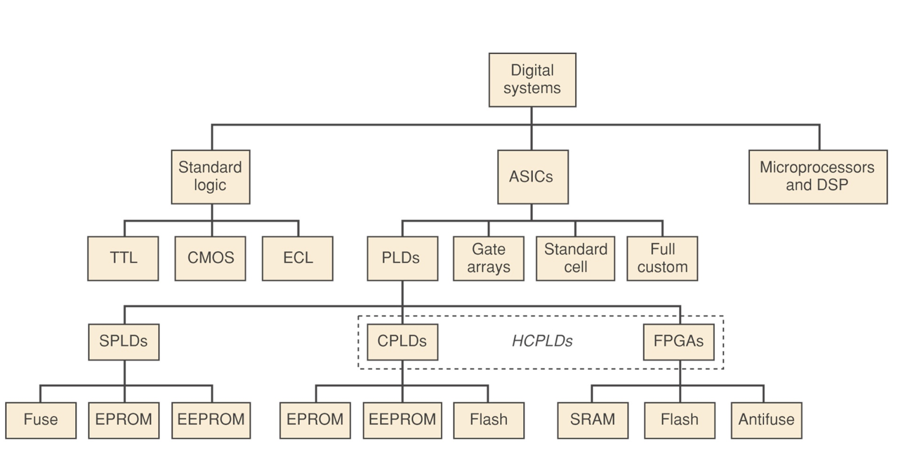

Árvore das Famílias de Sistemas Digitais

A funcionalidade de um circuito digital pode ser obtida empregando vários tipos diferentes de hardware(CIs). Pode-se empregar dispositivos lógicos padrões ou dispositivos lógicos programáveis para produzir a mesma função. Vários fatores devem ser considerados no processo de escolha, incluindo a velocidade de operação necessária do circuito, custo de fabricação, consumo de potência do sistema, tamanho do sistema, e ciclo de desenvolvimento do projeto, entre outros. Um projeto de sistema digital complexo pode incluir difrentes tipos de hardware.

A árvore das famílias de sistemas digitais mostra as opções disponíveis nas várias categorias de dispositivos digitais.

As principais categorias de sistema digital incluem lógica padrão, circuitos integrados de aplicações específicas (ASICs) e microprocessador / dispositivos de processamento digital de sinais(DSP).

A primeira categoria de dispositivos lógica padrão refere-se aos componentes digitais funcionais básicos (portas, flip-flops, decodificadores, multiplexadores, registradores, contadores, etc.) que estão disponíveis como chips SSI e MSI. Esses dispositivos têm sido usados ??por muitos anos para projetar sistemas digitais complexos.

A categoria de microprocessador / dispositivos de processamento digital de sinais(DSP) é uma abordagem muito diferente para o projeto de sistema digital. Na verdade, esses dispositivos contêm os vários tipos de blocos funcionais estudados. Com sistemas de microcomputador / DSP, os dispositivos podem ser controlados eletronicamente e os dados podem ser manipulados executando um programa de instruções do aplicativo.

A terceira categoria principal de sistemas digitais é chamada de circuitos integrados de aplicações específicas ASICs). Esta ampla categoria representa a solução de projeto de hardware moderno para sistemas digitais. Como o acrônimo indica, um circuito integrado é projetado para implementar uma aplicação específica projetada. Quatro subcategorias de dispositivos ASICs estão disponíveis para criar sistemas digitais:

- dispositivos lógicos programáveis(PLDs)

- matrizes de portas(gate arrays)

- célula padrão(standard-cell)

- totalmente personalizado(customizados )(full-custom)\

Dispositivos lógicos programáveis (PLDs), chamados de dispositivos lógicos programáveis em campo (field- programmable logic devices - FPLDs), podem ser configurados de forma personalizada para criar qualquer circuito digital especificado, desde portas lógicas simples até sistemas digitais complexos.

Matrizes de portas(gate arrays ou mask-programmed gate arrays - MPGAs) são circuitos ULSI que oferecem centenas de milhares de portas. As funções lógicas desejadas são criadas pelas interconexões dessas portas pré-fabricadas pelo fabricante. Uma máscara personalizada para a aplicação específica determina as interconexões da porta, de maneira muito semelhante aos dados armazenados em uma ROM programada por máscara.

Os ASiCs de célula padrão(standard-cell) usam blocos de construção de função lógica predefinidos chamados células para criar o sistema digital desejado. O layout do CI de cada célula é projetado anteriormente e uma biblioteca de células disponíveis é armazenada em um banco de dados de computador. As células necessárias são dispostas para a aplicação desejada e as interconexões entre as células são determinadas.

ASiCs totalmente customizados(full-custom) são considerados a escolha definitiva de ASICs. Como o nome indica, todos os componentes (transistores, resistores e capacitores) e as interconexões entre eles são projetados pelo projetista do CI. Isso pode resultar em CIs que podem operar na velocidade mais alta possível e exigir a menor área do CI(chip individual).

Geralmente, os PLDs podem ser descritos como sendo um de três tipos diferentes:

- dispositivos lógicos programáveis simples (SPLDs),

- dispositivos lógicos programáveis complexos (CPLDs) ou

- matrizes de portas programáveis em campo (FPGAs).

Um PLD, Programmable Logic Devices(Dispositivos Logicamente Programáveis), é um circuito integrado com um grande número de portas lógicas, flip-flops, e registradores que estão interconectados no chip.

Várias conexões de um PLD são elos fusíveis, semelhantes aos encontrados em PROMs e EPROMs, que podem ser queimados.A Fig. 1a mostra a estrutura básica usada pelos CIs logicamente programáveis: um arranjo de portas AND e um arranjo de portas OR, cujas entradas podem ser interconectadas para produzir funções nas saídas das variávies de entrada.

|

|

Para melhorar a representação dos dispositivos PLDs, adota-se uma simbologia simplificada onde as várias entradas de uma porta são representadas por uma única linha e as conexões das variáveis de entrada às portas são indicadas por um ponto ou um X: um X indica um fusível intacto; um ponto representa um conexão fixa(não pode ser programada). A falta de quaisquer desses sinais no cruzamento de duas linhas indica que não há conexão. A figura ao lado mostra um exemplo dessa simbologia. |

|

Fig.1b |

|

Os PLDs são chamados programáveis porque a função específica do circuito integrado para uma aplicação é estabelecida pela queima seletiva de alguns fusíveis e deixando outros intactos.Este processo chama-se programação porque produz o padrão desejado de interconexões entre portas, FFs, registradores, contadores, etc., conforme as instruções do usuário. O processo de queimar os fusíveis pode ser feito pelo fabricante ou pelo usuário, empregando um programador de EPROMs. |

Fig.1c |

| Um PLD é constituído de um arranjo de portas AND de entrada(decodificador) e um arranjo de portas OR de saída (codificador). Os arranjos AND de entrada podem ser conectados às variáveis de entrada para formar os termos produtos necessários. As funções de saída do circuito são obtidas interligando os termos produtos de saída do arranjo AND às entradas das portas do arranjo OR. |

|

Fig.2 |

Arquiteturas dos PLDs

Várias arquiteturas são usadas para CIs PLDs. A arquitetura mais comum e utilizada é a PROM. A Fig. 3a mostra uma PROM que funciona como um tipo de PLD.

Memórias Só de Leitura Programáveis(PROMs-Programmable Read Only Memories)

Nos dispositivos de memória só de leitura programáveis(PROMs), o arranjo AND é pré-definido em fábrica e somente o arranjo OR é programável.\

|

|

Para programar a PROM a fim de gerar a função O3 indicada, o primeiro passo é escrever a função como um soma padrão de produtos, conforme mostra a tabela verdade. Observe que a programação consiste em manter intactos os fusíveis dos mintermos cujas linhas tem 1 na tabela verdade e queimar os fusíveis nas linhas que iguais são 0. |

Fig.3c |

| Os arranjos PALs têm somente os arranjos AND programáveis enquanto os arranjos OR são pré-conectados em fábrica, então todas as portas AND podem ser programadas para gerar o termo produto das variáveis de entrada e seus complementos(Figura 5a). Como as entradas das portas OR são fixas, então limita as funções da saída ao número de mintermos ligados nas entradas das portas OR. Caso seja necessários mais mintermos para gerar uma função, não será possível programar. Embora sejam menos flexíveis que PLAs, as PALs são mais rápidas porque as conexões pré-configuradas levam menos tempo para chavear que as conexões programadas. |

|

Fig.5a |

A Fig. 5b mostra uma configuração típica para uma PAL com quatro entradas e quatro saídas. Sendo que cada porta OR tem suas entradas ligadas a quatro linhas de termos produtos, então só pode gerar funções de no máximo quatro mintermos.

|

|

Devido à variedade de arquiteturas, dispositivos FPGAs precisam de ferramentas de programação específicas do fabricante para a programação.

Características dos PLDs

Vários dispositivos PLDs têm saídas com buffers tri-state comandados por uma única linha de habilitação, requerendo apenas um pino de entrada do dispositivo.

|

Alguns dispositivos PLDs são construídos de modo que as saídas tri-state são realimentadas para as entradas do arranjo AND.

No exemplo acima, o PLA tem três entradas a, b e c e três saídas w, x e y, porém foi programado como quatro entradas e somente duas saídas. Observe que o buffer da saída y foi desconectado do sinal de controle de habilitação e ligado ao nível lógico alto, permanecendo sempre habilitado. A saída y está agora configurada como a quarta entrada da PLA.

Como as saídas w e x continuam a funcionar como funções de saída, então os elos fusíveis de realimentação são queimados para assegurar que não terão efeito nas entradas.

Certos tipos de PLDs são equipados com registradores nas saídas e outros com latches.Dependendo do dispositivo, os registradores(ou latches) podem ser fornecidos em todas as saídas ou em grupo de saídas. Em geral, é possível não utilizar os registradores de saídas através do uso de multiplexadores construídos no PLD.Este tipo de PLD é denominado sequenciador lógico programável.

|

|

Questões para Revisão Tente resolver on-line um teste sobre Dispositivos Lógicos Programáveis(PLDs). |

Visite estas páginas sobre PLDs |

|

|

Dispositivos de Lógica Programável (PLD’s) |

Atualizada em